# Reverse engineering PLEX-C code to SDL10 code

Martin Berg Dep. of Communication Systems Lund Institute of Technology

**Tutors:**

Magnus C. Ohlsson (Dep. of Communication Systems, LTH Lund) Jörgen Palm (Ericsson Radio Systems AB, Hässleholm) Henrik Cosmo (Ericsson Radio Systems AB, Hässleholm)

The telecom business is one of the fastest growing markets today. Many companies are fighting over the market shares and to be at the top of it, the companies have to make their product developments more efficient and with higher quality. Increasing one of these components will probably decrease the other. This can be avoided by using the reverse engineering technology. It can be applied on a system to increase the quality, shorten the development time, or both. In this thesis we discuss different ways to increase quality and shorten the development time, by applying reverse engineering. One solution can be a software programming language change, and the new language may describe the system at a higher level of abstraction. It is that solution we have focused on in our work. Parts in Ericsson's GSM system is converted from their old programming language PLEX-C to the graphical programming language SDL10. The purpose is to develop features in the SDL10 environment in the future, which will both increase the quality and shorten the development time. Conversion between two programming languages is not an easy task. The differences between the two languages address some problems. These problems and solutions to them are discussed and presented in this thesis.

Abstract

| CHAPTER 1 | INTRODUCTION                  | 1  |

|-----------|-------------------------------|----|

|           | Overview                      | 1  |

|           | Our work                      |    |

|           | Organization                  |    |

|           | Reading guidelines            |    |

| CHAPTER 2 | PROBLEM STATEMENT             | 5  |

|           | Background                    | 5  |

|           | Problems                      |    |

| CHAPTER 3 | Related Work                  | 7  |

|           | Reverse engineering           | 7  |

|           | Methods                       |    |

|           | Related activities            |    |

|           | Redocumentation               |    |

|           | Design recovery               |    |

|           | Restructuring                 |    |

|           | Re-engineering                |    |

|           | Tools                         | 11 |

|           | Compilers                     | 11 |

|           | Restructurers and beautifiers |    |

|           | Translators                   | 12 |

|           | Parallizers                   | 12 |

|           | CASE tools                    | 12 |

|           | Balance between reverse and forward engineering             | 13 |

|-----------|-------------------------------------------------------------|----|

|           | Practical use of reverse engineering                        |    |

|           | Year 2000 problem                                           |    |

|           | Data reverse engineering [P8]                               |    |

|           | Data conversion [P7]                                        |    |

|           | PL/IX - C++ [P6]                                            |    |

|           | SDL Reverse [I6]                                            |    |

|           | KomPlex [I8]                                                |    |

|           | SPOT [I9]                                                   |    |

| CHAPTER 4 | PLEX-C                                                      | 21 |

|           | History                                                     |    |

|           | 5                                                           |    |

|           | Versions                                                    |    |

|           | System<br>Standard                                          |    |

|           | Standard                                                    |    |

| CHAPTER 5 | SDL                                                         | 25 |

|           | Description                                                 | 25 |

|           | History                                                     | 25 |

|           | Benefits                                                    | 26 |

|           | Telelogic Tau                                               | 26 |

|           | SDLtool                                                     | 28 |

|           | The SDL language                                            |    |

|           | Components                                                  |    |

|           | The layout of SDL                                           |    |

|           | SDL10                                                       | 31 |

|           | MSC                                                         | 32 |

| CHAPTER 6 | COMPARISONS - SDL VS PLEX-C                                 | 35 |

|           | Similarities                                                |    |

|           |                                                             |    |

|           | Differences<br>Conclusions for similarities and differences |    |

|           | Conclusions for similarities and differences                |    |

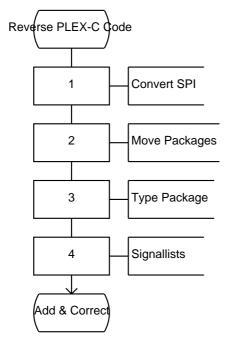

| CHAPTER 7 | REVERSE PLEX-C CODE                                         |    |

|           | Block division                                              | 40 |

|           | Reverse tool unsupport                                      | 41 |

|           | Automatic generated code                                    |    |

|           | Time estimation                                             |    |

|           | Reverse tool in our work                                    |    |

|           | Problems                                                    | 43 |

| CHAPTER 8  | CONCLUSIONS                                | 47 |

|------------|--------------------------------------------|----|

|            | Differences                                | 48 |

|            | Future                                     |    |

|            |                                            |    |

| CHAPTER 9  | ACKNOWLEDGEMENTS                           | 51 |

|            |                                            |    |

| CHAPTER 10 | References                                 | 53 |

|            | Public Resources [Px]                      |    |

|            | Internet Sites [Wx]                        |    |

|            | Internal Ericsson documents [Ix]           |    |

|            |                                            | )+ |

| APPENDIX A | GSM / BSC                                  | 57 |

|            | History                                    | 57 |

|            | Techniques and restrictions                |    |

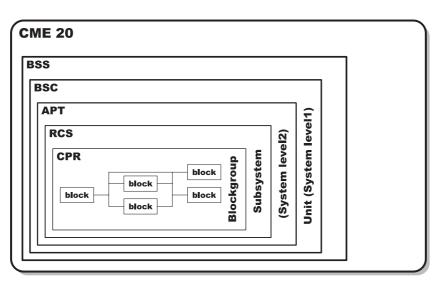

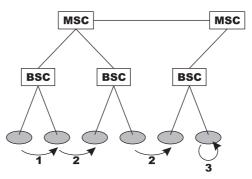

|            | Structure                                  | 58 |

|            | BSC                                        | 59 |

|            | Function explanations                      | 61 |

|            | Paging                                     | 61 |

|            | Handover                                   | 62 |

|            | Signalling connection setup                | 62 |

|            | Assignment                                 |    |

|            | Resource level supervision                 |    |

|            | Cipher mode control                        |    |

|            | Classmark distribution                     |    |

|            | Transfer of BSS transparent messages       |    |

|            | Short message service (SMS)                |    |

|            | Connection release                         |    |

|            | Traffic event measurement in radio network | 04 |

| APPENDIX B | ABBREVIATIONS                              | 65 |

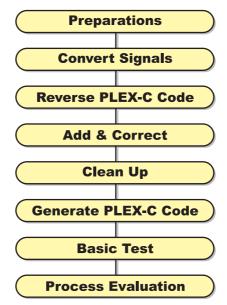

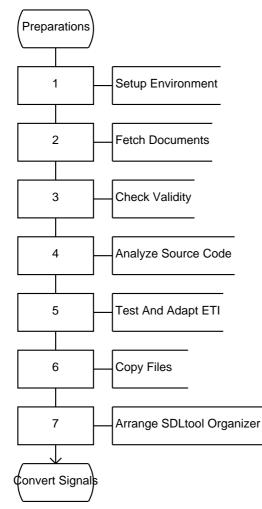

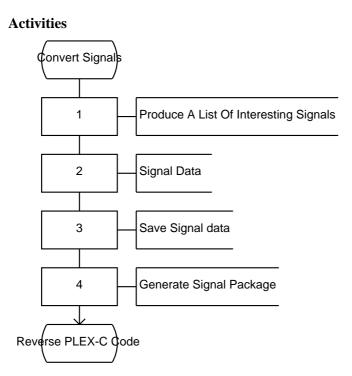

| APPENDIX C | CONVERSION PROCESS                         | 69 |

|            | Time estimations                           | 70 |

|            | Activities                                 | 70 |

|            | Preparations                               | 71 |

|            | Convert signals                            |    |

|            | Reverse PLEX-C code                        | 79 |

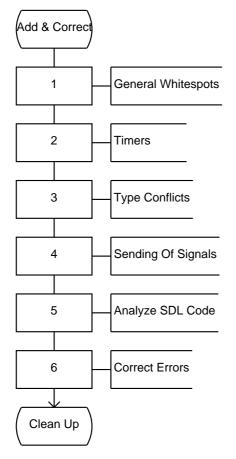

|            | Add and correct                            |    |

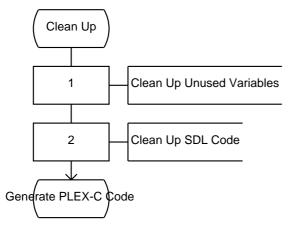

|            | Clean Up                                   |    |

|            | Generate analyzed PLEX-C code              |    |

|            | Basic Test                                 |    |

|            | Process evaluation                         | 90 |

$\bigcirc$

# 1.1 Overview

The telecommunication company *Telefonaktiebolaget LM Ericsson* has reached far with their AXE exchange. It is installed for telephone services all over the world and is still under development. When Ericsson decided to go into the wireless telecommunication area, they built their platforms (NMT, GSM, etc.) based on the AXE system. Of course, modifications were made, but the main concept of AXE was still there [11].

It has gone many years since the AXE system was born, and they use the same programming language. When a system is maintained, it gets larger and larger formatting. Maintenance will be harder and the source code in the system can get confusing. Confused means that the flow in code is hard to follow and it is difficult to understand the functionality. Different methods exist to solve the problem, but since the programming language that Ericsson uses when developing services in their systems has its origin in the 1970's, a programming language change may increase quality. By increasing the quality we mean lesser defects in both released and under development systems. Today "clean-ups" (rewriting code to remove the confusing part) has to be made after that about two or three projects have modified existing code. This is expensive, both in time and money.

Ericsson has found a programming language that they want to investigate for further use in new projects, SDL (Specification and Description Language). SDL has many benefits compared to their old language that they use today, PLEX-C (Programming Language for EXchanges, C-version). PLEX-C is a real-time programming language that Ericsson self has developed. It looks a little like Pascal, but the differences are many. SDL is graphical, with other words one "draws" the programs with help from a tool. The graphical interface makes the source code more understandable and easier to overview. Other benefits are

shorter development time and thereby lower development cost. The quality will be increased due to a more structured and formal development model, i.e. no manual coding and testing at higher level of abstraction earlier in the development process. Ericsson also has some parts that are designed in the programming language C, and in SDL both PLEX-C and C code can be represented at the same time (SDL is platform independent). More benefits are described in section 5.3.

Changing programming language is not easily done. PLEX-C and SDL does not have the same level of abstraction, i.e. SDL is a high-level programming language and PLEX-C is a low-level language. This is not the only reason for the complexity, differences in variable formats, signalling and not to forget the real time requirements. Time critical functions can in PLEX-C be written in the assembler language that PLEX-C code is compiled to, ASA, for optimizing the specific function. This must also be converted correctly. (Assembler is a programming language that is hardware dependent, i.e. each assembler statement corresponds to a single machine instruction.)

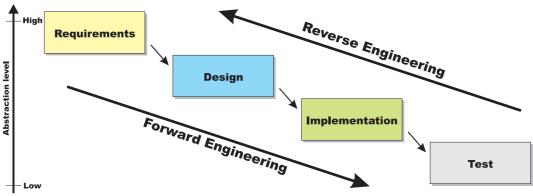

Converting from one abstraction level up to a higher is called *reverse engineering*. The reverse engineering area is large and increases fast. Much research effort is put here because, among others, many systems were developed during the 1970's and the designers did not think about the millennium change 25 years ahead. Reverse engineering can be used to solve problems related to the year 2000 problem (see section 3.6.1). Other things that reverse engineering is used for are clean-ups and maintaining systems. Ericsson uses clean-ups on their systems today, but since they cost more and more (the systems grow) and the fact that Ericsson uses an old programming language, make the profit for changing language higher.

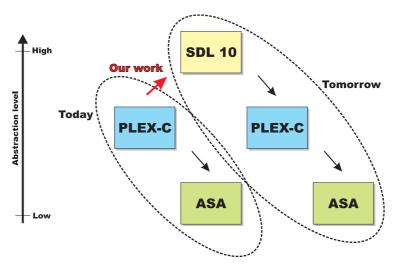

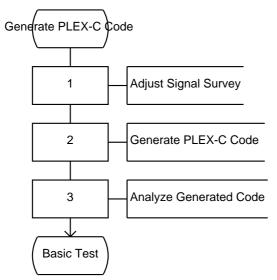

# 1.2 Our work

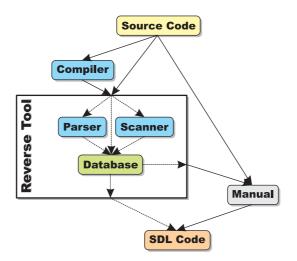

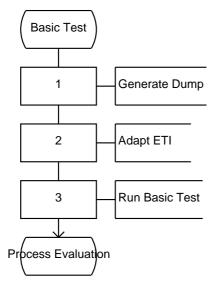

If Ericsson changes their programming language, they cannot manually convert all old source code into SDL, it would take too long time and cost to much. Instead this has to be done automatically with help from a *reverse tool*. To see if the reverse tool is feasible, the SDL code is compiled back to PLEX-C code and there tested with the same test rules that is used for normal development in PLEX-C (see figure 1). Defects found here can have their origin either from the reverse tool or from the compiler (SDL to PLEX-C). Since the compiler is tested before, and there are test possibilities at SDL level, separation of the two kinds of defects will not be difficult. Defects from the compiler are not of interest for our work.

Even though that the reverse tool is working correctly, it is no guarantee that all parts in the system can be converted. If this is the case, these parts have to be converted manually. The parts that are impossible to convert automatically and why, are of interest for our work.

We have in our work focused on the consequences of the differences between the two languages (PLEX-C and SDL), i.e. what is difficult to convert and why. Since the differences are not represented in one single block, two blocks with different purpose have been converted.

Figure 1. Our work in the software development

# **1.3 Organization**

In **chapter 2** the questions that our work discusses are stated. **Chapter 3** briefly describes reverse engineering and other related work. Projects similar to our work are described too. In **chapter 4** and **5** the two programming languages PLEX-C and SDL10 are described. It is between these two languages transformations are done. **Chapter 6** describes and discusses the similarities and differences between PLEX-C and SDL. It is the differences that are of interest for our work. **Chapter 7** describes the tool that we have used in our work, and the major problems that we found when reverse engineering. In **chapter 8** our conclusions are stated, and future work is discussed. **Chapter 9** is acknowledgments and **chapter 10** is references.

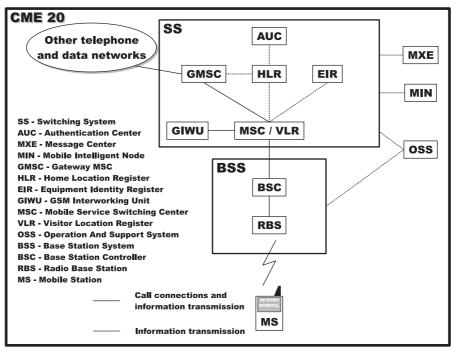

**Appendix A** describes an overview of Ericsson's implementation of the GSM system, CME20. Our work is tested deep down in this system and exactly where is also described here. In **appendix B** abbreviations found in this thesis are described. **Appendix C** describes a process for how to make a conversion project.

# 1.4 Reading guidelines

Depending on your knowledge of the different subjects in our work, not all chapters are necessary to read, or not of interest for you. The reader must be familiar with the substance of chapter 6 to understand some parts in chapter 7 though, and the process script in appendix C is written on the basis that the reader has knowledge about Ericsson's development process and terms belonging to it.

### 1.4.1 Designer

The designer is the person who's interest is executing the process described in appendix C. Interesting parts for him/her may be chapter 3 for some background knowledge of reverse engineering and what different types of conversions that have been done before, chapter 4 and 5 if he/she has limited knowledge of the programming languages (PLEX-C and SDL), and chapter 6 and 7 to understand the problems that may occur while executing process.

### 1.4.2 Test engineer

The tester is a person that test the interrelationships between blocks. To write good test cases he/she could be interested in reading the following chapters. Chapter 3 for back-ground knowledge about reverse engineering and what that involves, chapter 5 if the tester does not have knowledge of the SDL environment (he/she is probably well familiar with PLEX-C and does not need to read chapter 4), chapter 6 and 7 may be interesting because of their description of the differences between the two languages and problems that may occur when executing a conversion.

### 1.4.3 Reverse tool purchaser

If the reader only is interested in the reverse tool evaluation, chapter 2, 6 and 7 could be useful reading. Lack of knowledge within the programming languages, chapter 4 and 5 may also be interesting reading. By reading these chapters, he/she will understand why we executed our work and gain knowledge about executing a programming language change process.

### 1.4.4 Quality manager

A quality manager may be interested in chapter 2 to understand why our work was executed, chapter 3 to gain knowledge about reverse engineering, chapter 4 and 5 to understand the two programming languages, chapter 6 and 7 to gain knowledge about the problems that a conversion brings, and finally chapter 8 to achieve our conclusion about reverse engineering source code.

# 2.1 Background

Today PLEX-C is used as programming language when developing and maintaining parts in Ericsson's CME 20 system (Ericsson's implementation of the GSM standard, see Appendix A). The language is old and today there are several other languages that fulfil Ericsson's requirements. One of them is SDL. SDL has many benefits towards PLEX-C, and they are described in section 5.3.

Changing programming language is not an easy task. There are many differences between the two languages that must be considered. The conversion is not made for the whole system at one time, instead parts called blocks are converted one at a time. Blocks can be divided into different categories depending on their task. To convert a block, a conversion tool, that handles most of the problems, will be used. But some questions still remain.

# 2.2 Problems

These questions are discussed and answered in this thesis:

- **1. Is it possible to apply reverse engineering on PLEX-C blocks?** The tool that we will use for the conversion, does it work properly, or has it defects? If there are defects, how do they affect the conversion?

- **2.** If it is possible, on what type of blocks can we apply reverse engineering? Since the blocks can be divided into different categories depending on their task (described in section 7.1), maybe all blocks not are convertible. If there is a difference in convertibility, what are the reasons for this?

#### 3. How long time will it take to convert a special block?

Is it difficult to convert a block, and how automized is it? Are there differences between different kinds of blocks, or is the converting time just depending on the size of the block?

#### 4. How is the reverse engineering applied to blocks?

This question will be answered with a process script that explains step by step how to do when converting blocks from PLEX-C to SDL.

Notice that the conversion is only done block by block and how they are connected to each other is not a part of our work.

# 3.1 Reverse engineering

When developing everything from small programs to large systems, the development process can be divided into different phases. A process may consist of the phases requirements, design, implementation and test (see figure 2). This is a natural order for development of anything, because first one thinks of the products overhead functions, and later on more and more on detailed specifications of how the functionality will be implemented. This is called *forward engineering*, i.e. go from a high level of abstraction to a lower level.

Figure 2. Forward and reverse engineering

The opposite to forward engineering is *reverse engineering*. The purpose of reverse engineering can simply be described as taking a product apart to learn how it works, or in other words, study a system and make a specification of it at a higher level of abstraction. One

example is making a design-document from C code. Reverse engineering is a term that refers to an analysis process which is done with help from methods and tools that investigate the system, its components, and their interrelationships. *Program understanding* or *program comprehension* are two other terms for reverse engineering that say more about what it is.

The origin of the term reverse engineering comes from the hardware technology, where it was used, among others, to duplicate other companies hardware products. Now this has shifted to software since it has become a larger part of whole systems with both hardware and software. In [P12] M. G. Rekoff defined reverse engineering (denoted to hardware technology) as

"the process of developing a set of specifications for a complex hardware system by an orderly examination of specimens of that system."

Five years later Chikofsky and Cross wrote [P4]:

"Reverse engineering is the process of analyzing a subject system to identify the system's components and their inter-relationships, and to create representations of the system in another form at higher levels of abstraction."

The two definitions above say exactly the same thing, but about different domains. This shows how close the domains are and similar methods can thereby be used when reverse engineering in the software world as in the hardware. In the hardware world reverse engineering is traditionally used to duplicate systems, while in the software world it is used to raise the abstraction level. Our work is within the software domain.

There are many reasons to use reverse engineering, and some may be [P11]:

- Improve the quality of one's own products.

- Analyze competitors' products to achieve knowledge of some of their secrets.

- Discover hidden defects in a newly developed product.

- Gain basic understanding of a system and its structure.

# **3.2 Methods**

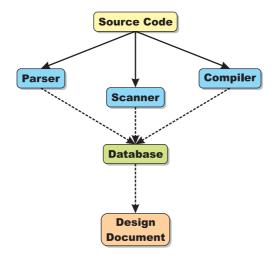

Reverse engineering can be seen as a set of methods and tools. The methods describe how reverse engineering should be done and the tools do it. Figure 3 shows an overview of the reverse engineering process. Information is retrieved from the source code by parsing and scanning it. The information is stored in a database in an organised way. Compiling the source code may also provide valuable information. The information is hidden in the object code and the cross reference tables (both from compiler), and is also stored in the database. Together, all information in the database describes the source code, and a new document can be produced. The document can present the information, or describe the source code, as the user likes, for example the description can be textual, flow charts, dia-

grams, etc. The important thing is that it describes the source code at a higher level of abstraction, which makes it to a design document.

In figure 3, the dashed lines corresponds to "information from" and not raw data, which the normal lines represent.

Figure 3. Reverse Engineering - The process and abstraction differences

A method corresponds to how the source code is investigated (parser, scanner, compiler), how the information achieved by the investigation shall be presented, the database structure (object oriented or not), and how the database should be investigated to produce desired design documents [P11].

The simplest method is light examination of hardware. The engineer investigating the product may not even know that he is reverse engineering. During the investigation he builds models of the product and how it works. The models may be notes, diagrams, or just mental images and plans. This method, as many of hardware corresponding methods, have no tool support. Tools are simpler to develop and implement in the software domain, and therefore the methods there are more sophisticated.

# 3.3 Related activities

Put reverse and forward engineering together, and add some purpose for applying them, then four activities can be stated. Except for purposes, the differences are denoted to the size of the reverse respectively forward engineering part. For example, the reverse part can be so small that the designer can hold the information in his head, or as large as several design documents. Since the differences between the activities are more on the purpose plan rather than practical, it is hard to make sharp lines between them. Chikofsky and Cross have described the activities in [P11].

### 3.3.1 Redocumentation

Redocumentation is the simplest and oldest form of reverse engineering, and can also be described as a weak form of restructuring (see below). The difference, towards reverse engineering, is that redocumentation does not change the abstraction level, instead it produces new representations of the system considering other point of views.

The intention with redocumentation is to improve the comprehension of a system and create additional views that were not created in the original forward engineering process. Redocumentation tools present facts about a system in another form, but without migrating between development phases. Examples of redocumentation tools are *pretty printers* (displays a code listing in an improved form), *diagram generators* (creates charts from code by reflecting control flow, code structure or data structure), and *cross reference generators* (produces index over the variable use in the program).

#### 3.3.2 Design recovery

When reverse engineering, only the system itself is input to the process, but by adding existing design documentation, personal experience and knowledge about the problem and application domains to the input, fully describing documents at higher level of abstraction can be produced. This is called design recovery. The intense is to reproduce information required for a person to fully understand what the system does, how it does it, why it does it, etc.

#### 3.3.3 Restructuring

Restructuring can be seen as a more advanced form of redocumentation or a special form of reengineering. The latter when reengineering without adding new functionality. The difference compared to redocumentation is how the redocumented, or restructured system is presented, and if the new version is presented in a different way according to its origin, the activity is restructuring. The new version is usually at the same level of abstraction as the origin, and the semantic behaviour and the functionality is the same, i.e. no new functionality or changes are provided when restructuring. If SDL and PLEX-C had been on the same level of abstraction, our work would be about restructuring instead of reverse engineering, but since SDL has a higher level of abstraction than PLEX-C, reverse engineering is the right terminology for our work.

Restructuring is done to improve a systems structure and make it more understandable. Often the term is used as a synonym for reproducing a program from an unstructured form to a more structured form (code-to-code). This may be transformation from "spaghetti code" (lots of goto statements) to more structured code with less goto statements. But the term has a broader meaning, for example data normalization, which is a data-to-data restructuring transformation and is done to improve the logical data model in the design process.

Restructuring can also be performed without knowledge of a systems structural form and without understanding its meaning. An example of this is a conversion of a series of if statements into a case statement, or vice versa.

### 3.3.4 Re-engineering

Reengineering is restructuring with functionality changes implemented. Actually it is a combination of forward and reversed engineering. First, reverse engineering is applied to gain more knowledge of the system and make design documents. New functionality and changes to the existing can then be applied. Finally, forward engineering is used and the system is re-implemented with the new/changed functionality.

# **3.4 Tools**

Reverse engineering methods are constantly developed to be applied on systems for different reasons. To make it as easy as possible for the engineer, corresponding tools are developed as help and guidance, or to do parts of the reverse process. As with methods, tools can handle one or several parts shown in figure 3, often several. Actually it is only one of the parts that is developed as a single tool, the compiler. A reason can be that its origin is not within the reverse engineering domain, but in the forward engineering.

As with the methods, many different tools for different purposes have been developed. The compiler tool is the only tool that corresponds to a single symbol in figure 3, and the other may correspond to several symbols including dashed lines.

More information about the tools described here can be found in [P9], and more information about CASE tools can be found in [P11].

### 3.4.1 Compilers

This tool is the most used reverse engineering tool today. There are several reasons for this. Compilers must understand the source program well enough so the compilation not change the programs functionality, if the compiler has an optimize function, it must understand the source program even better. Optimizing changes are larger and more complex than normal compiling. Some compilers can also understand what type of faults that the designer has introduced in the code and may also suggest solutions, some generates cross reference tables, warnings of portability problems (problems according to different target machines) and not initiated variables that may cause errors. Most of the compilers also have a debugging function. To support all this, the compiler must know the source program very well.

### 3.4.2 Restructurers and beautifiers

The purpose of using restructurers and beautifiers is to improve the comprehensibility of a system. These techniques are used on older programs or programs written in an old version of a software programming language that maybe not have constructs that exists today, for example the while loop construct does not exist in early versions of Fortran [P11] and are implemented with goto statements. By restructuring the program so it is implemented in a later version of Fortran, the goto statements are replaced. Goto statements are today "forbidden" and recognized as "spaghetti programming". By replacing them, the program gets more understandable.

Beautifiers are a little more complex than restructurers since they also know the coding standard, i.e. layout rules, that the user wants. This can for example be indentation, bracketing conventions for compound statements, spaces in expressions etc. Beautifiers are used when standardizing the layout within large systems that have had small amounts of maintenance, and/or numerous of designers that works with different coding standards.

### **3.4.3** Translators

Translators are tools that convert source code from one software programming language to another, for example the PLEX2SDL reverse tool. If the languages are at the same level of abstraction (optimizing) the most common is that the new code is less readable, but if the new language is at a higher level of abstraction and the conversion is successful, the tool can produce a more understandable and modular program.

### 3.4.4 Parallizers

Parallizers are applied on programs that will be run on parallel computer systems. They make the code more effective by, among others, replace loops with single statements that simultaneously work on several elements in an array. The result is smaller and more readable source code which is specialized for a certain hardware.

### **3.4.5 CASE tools**

As with compilers, CASE tools were first developed to support developers within the forward engineering domain. CASE is the abbreviation for *Computer-Aided Software Engineering* and represents a set of products, services and technologies for software development. CASE is for software engineers what CAD (Computer-Aided Design) is for constructors (e.g. ship-, space-, aircraft-constructers). The reason for developing such a tool is based on that not much effort were put in documentation and designing in the early years of 1970's. Software systems were growing fast and more control over their development were desired and concurrently the faults had to decrease since they were the most cost inefficient part in the development phase. This concluded in that more and more effort were put earlier in projects. Methods saying how to run software development projects were "invented" and tools helping designers follow the methods were also produced

(CASE tools). Since then CASE tools are getting more and more efficient and gets more and more functionality.

At the beginning of the 1990's, it was discovered that CASE could be used when maintaining systems, and thereby also when reverse engineering systems.

A CASE tool consists of a graphical editor, consistency checkers and may also have a code generator. The graphical editor is used to present the high level design graphically and not textual. The consistency checker is used to test the system and the code generator can produce the code, or at least a part of it.

CASE tools that have the ability to reverse engineer systems can in most cases produce the graphical pictures of the high level design automatically. These pictures can represent different diagrams depending of what knowledge one wants about the system. Since this is a topic in great research, more diagram types and further analysis will come in the future. Some types of diagrams can be:

#### • Structure chart

This diagram is the most common today and shows the subprograms and how they are connected to each other.

• Data flow diagram

This diagram shows the major software modules and data allocation, and how data and control information flows among them.

#### • Entity relationship diagram This diagram describes major external sources, data and modules that uses them.

### 3.5 Balance between reverse and forward engineering

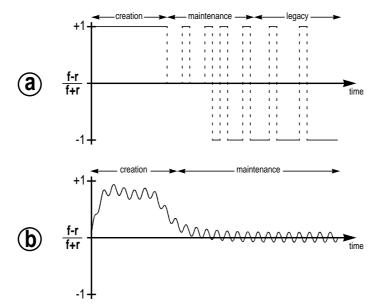

It is expensive to reverse engineer a system, but it is also expensive not to do it. The maintenance cost is increasing as the system gets older, because the maintainers must understand the system to be able to maintain it. This means that ideally a defined balance between forward and reverse engineering has to be found. van den Brand et. al. has taken a closer look at program development regarding forward and reverse engineering [P3]. Figure 4 shows different phases of the life cycle for a software system, **r** and **f** are a measure for the reverse respectively forward engineering effort. **a** shows the classical life cycle and **b** the desired life cycle of software systems.

Figure 4. Differences between a. classical and b. harmonic software engineering

#### Creation

**a.** Only forward engineering is used in this phase, which is the classical way when developing software systems.

**b.** Reverse engineering is used directly at the start of the development, combined with forward engineering, to influence the design. This could for example be to study the impact of different implementation alternatives. One can say that this is a reverse engineering driven software development.

#### Maintenance

**a.** To keep the system running small amounts of maintenance is needed, and the amount will increase. The forward engineering is interrupted by larger and larger reverse engineering periods.

**b.** As in classical software engineering, maintenance is needed in the harmonic software engineering to keep the system running. The knowledge about the system is kept up to date with reverse engineering, and maintenance is done with the forward engineering.

#### Legacy

a. When the reverse engineering takes to much time, the maintenance is hard to keep up. The maintainers are working more on understanding the system instead of maintaining it.b. The reason of harmonic software engineering is to skip this phase, and thereby have a product with lesser defects and longer lifetime.

By using the facts that van den Brand et. al discusses in [P3], better systems that are easier to maintain will be produced. Reverse engineering will also be a larger part in software engineering in the future.

# 3.6 Practical use of reverse engineering

Many reasons why reverse engineering should be applied on a system exists and in this section both reasons for reverse engineering a system and reverse engineering projects are described. A strong connection exists to related activities described in section 3.3.

### 3.6.1 Year 2000 problem

In many computer systems, only two numerals are used two define a certain year, e.g. 87 for 1987, and some of these systems uses this numerals to count a difference between two years. This is no problem as long as the numerals represent years within the same century. Let us say that you want to calculate someone's age. You know the year of birth, 1946, which is represented as 46 in the computer system. To calculate the person's age, 46 is subtracted from today's year. The age will be 99 - 46 = 53 years. Next year (2000) the equation will be 00 - 46 = -46, which is an incorrect answer. In some systems negative numbers cannot be stored and a failure will occur. If so the user of the system is alerted and can correct input data or calculate the data himself. But if a wrong value is stored and used in further calculations, final output data will be corrupt and that is not always discovered by the user. Other faults that may occur can be wrong decisions made by the computer system which will conclude in for example that railroadpoints are set wrong (how and if the year is involved in railroadpoints or not, is not a part of this thesis).

The year 2000 problem is complicated. It is hard to find and can be found in many systems. Many companies put major resources to solve this problem. By using reverse engineering to raise the abstraction level of a system, knowledge about what parts that may be affected by the millennium change can be achieved. These parts can then be re-designed so they can manage the problem. But the largest problem is the cost in money, personnel and especially time, it has to be solved before the turn of the year 1999 - 2000.

#### 3.6.2 Data reverse engineering [P8]

The reason for applying reverse engineering at systems to solve their year 2000 problem is done because one wants to get data about the data inside the system. This retrieved data is called metadata (see section 3.6.3). The metadata is not only used to solve the year 2000 problem.

Today, with rougher competitions between companies, each company must achieve as much valuable information as they can from data that they already have. This data can be statistics over customers etc. The problem is that many companies have lots of data, but they do not know that these data holds valuable information for them. Example of such data can be what, when and how much customers buy, if the customer pays with a credit card, etc. The data can be stored in different ways, for example locked in systems whose designers retired long time ago, in applications that were produced as a temporary fix, but have been in use ever since or even as data that the organization does not know that it has.

Organizations need to have the right data and it is important that they also know what it has, were to find it and most of all know what it means. To retrieve the valuable information from the data, one can apply reverse engineering and collect metadata. The metadata helps the organization to understand it's data.

### 3.6.3 Data conversion [P7]

The departments of Personnel and Training (DP&T) and Accounts (DOA) at the Commonwealth in Virginia wanted to replace their existing payroll and personnel information systems because they had become inefficient, too expensive to operate and maintain, and the management were concerned about keeping the staff up to date with the technical knowledge of the databases. The system consisted of two large databases and software to manage them. The databases were not integrated, which the departments wanted so they could merge payroll and personnel records. A new system consisting of three modules from *PeopleSoft*, was decided to replace the old one. PeopleSoft's modules are build specially for server - client applications and should be tailored to fit each organizations need. This is what the departments wanted. The problem was to move the data from the old databases to the new ones. It was a large amount of data to move. A tool that could convert the data had to be developed. To know how to convert the data, more information about the databases, both old and new ones, were needed. This information (data about data) is called *metadata*. To get the metadata reverse engineering were used. To manage all metadata that this project produced, a new database and handling procedures called *The Meta*data Access Tool (TheMAT) was developed. It uses Microsoft Access with both automated and manual procedures. The metadata were later on used to map corresponding information in the two systems (the old and new).

This restructuring project ended successful and the conclusions were that it was not so expensive as expected to use metadata for developing data conversion tools and the metadata itself can be maintained easily with tools. Some metadata can be maintained by using a CASE tool (see section 3.4), especially if such a tool were used when developing the system. Metadata that easy can be created and maintained can be a valuable asset.

### 3.6.4 PL/IX - C++ [P6]

Reverse engineering, or rather restructuring, is a useful activity when changing software language. In a project funded by IBM and project members from universities of Waterloo, Victoria and Toronto, PL/IX (pronounced PL nine) source code should be converted to C++ code using reverse engineering. PL/IX is a programming language that IBM uses and to simplify maintenance and make further development of the system easier, IBM wants to change software language. From the Universities point of view the project was an experiment to see how hard it is to make a software language converting tool.

To compare and to be able to map constructs (if, for, etc. statements) and structures (variable types) between the two languages an abstract syntax tree (AST) were produced with help from a custom built PL/IX parser and linker (compare with compiling). Defined con-

structs and structures were sorted into different domains. If one construct or structure in PL/IX did not have a corresponding item in C++, a new one had to manually be added to the domain library.

In the first half of the project the converting was manually performed and in the second half a semi automatic tool was used. When the project was finished, the tool still was semi automatic and some parts had to be converted manually. The conclusions from this project was that it is possible to develop tools that decrease the manual effort in a software language change.

### 3.6.5 SDL Reverse [I4]

When Ericsson choosed to investigate the possibility to change software language in their GSM system from PLEX-C to SDL10 they soon realized that it was impossible to change all source code manually. A conversion tool was required. A project started to develop such a tool, *SDL Reverse*. Unfortunately the inexperience, the bad estimations and mostly the fact that the task actually is hard to manage made the project fail. Instead another company took over the development of the "*Reverse tool*". They are now almost finished with it and it is this tool that we have used in our work.

This project's purpose was to develop a tool which reverse engineers a system. The project itself is about forward engineering, but inside the produced tool the activity can be classified as either reverse engineering or re-engineering, depending on the point of view. The tool reverse engineers the system to achieve information about it and then implements the information in another software language. The information is at a higher level of abstraction than the new implementation, and forward engineering is used. Merging the processes concludes in re-engineering. But from another point of view where the tool is seen as a black box performing the transformation, the activity is reverse engineering.

### 3.6.6 KomPlex [I5]

Our work is not the only project that have tested the reverse tool, the KomPlex project, finished in the summer of 1999 at Ericsson's department in Aachen, Germany, has also tested it. The project's purpose was to evaluate and test the reverse tool and see what kind of blocks that could be converted, but also to evaluate if Ericsson should continue with reverse projects and thereby make a software programming language change. Problems with the tool was reported during the project to the producer, and some of them were fixed during the project.

The project was intended to convert eight blocks but they tried out 21 blocks where 16 were successfully converted and 5 failed for different reasons. A conversion is successful when it passes a test that tests at least 80% of the code. The failure reasons can be unimplemented support in the reverse tool for some kind of constructs in PLEX-C. A connection can be seen if the blocks are divided into groups. The division is made on basis of the

blocks' tasks since the structure of a block depends on its task (see section 7.1). The categories are:

- Traffic blocks

- Message handler blocks

- Database blocks

- Command blocks

To analyse and see if successfully converted blocks can be accepted in the system, more aspects than testing the code has to be done. Measurements of the new code size (number of lines), the data storage size (e.i. the variables total space) and effectiveness (execution time) were done. On the basis of these measurements the following conclusions have been reached.

*Traffic blocks* seemed to manage best. The regenerated code size and data storage, and execution time were all within the 10% characteristic limit. The regenerated code from *Message handler blocks* increased with 17% which not is acceptable. The execution time is just above the limit (11%). The reverse tool will be updated to handle this problem. *Database blocks* were also slightly above the limit, but optimizations in the SDL2PLEX generator will solve this problem in the future. The block category that was hardest to manage were *Command blocks*. Only one block were possible to convert successfully but the same tendencies could be seen in the unsuccessfully converted blocks. The data storage increased with over 100% and regenerated code size became 50% larger. Although these blocks are small compared to other blocks and they are not so time critical, also updated reverse tool to decrease these figures will make it possible to convert this blocks in the future.

The conclusion from this is that after updates to both the reverse tool and the SDL2PLEX generator mostly all blocks will be able to convert.

Also a small formula for estimating how long time it will take to convert a block has been produced. It considerates only the number of PLEX-C statements to convert though. This formula is tested within our work.

The members of the project had different experience, some PLEX, some SDL and some both. This composition of people with different knowledge appeared as a good prerequisite when running such a project.

The KomPlex project has answered most of the problems that our work is bringing up, but the structures inside different blocks at different departments within Ericsson are not the same and therefore cannot all results from one project just be copied to another. Of course some considerations of the results will be made, but own experience at the departments are needed. The KomPlex project was also larger with both more personnel, more time and more blocks to convert than our work.

### 3.6.7 SPOT [I6]

To get some experience of converting PLEX-C blocks to SDL10 at Ericsson's department in Hässleholm, the SPOT project started in December 1997. The task was to convert a block into SDL10. The reason was to evaluate if a software language change could increase quality and decrease lead time for future projects. Also the SDL2PLEX code generator was evaluated according to capacity, memory size (data storage) and readability (the regenerated PLEX-C code must be readable for a human). Since the reverse tool did not exist at that time, the conversion was made manually. The conclusions were that all in the project thought that a software language change will shorten lead time and increase quality. The overall impression of SDL10 was good and that it was easy to use. The SDL2PLEX code generator on the other hand did not satisfy the expectations. Lots of improvements had to be made and a list of needed improvements were produced.

The differences between this project and KomPlex are small, both converted PLEX blocks to SDL10, but this project did it manually. Since a higher level of abstraction than the destination implementation were reached during the project, it should be classified as reengineering.

**Related Work**

# 4.1 History

The high-level programming language PLEX (Programming Language for EXchanges) was developed for Ericsson, by Ericsson in the 1970's, and later extended in 1983. The reason why Ericsson developed a new programming language of their own is simple - no other languages that fulfilled Ericsson's requirements existed. It had to be a high-level, real-time language with very strict requirements regarding real-time performance. The structure should be modular and the modules should communicate with different signals. All this is implemented in PLEX. PLEX is only used for telephony purposes, but it exists in thousands of exchanges all over the world, and it is also used by thousands of designers. PLEX is a company specific programming language, i.e. only one company uses the language in development, and that makes is hard to find documents describing the language. More information can be found in [I3].

# 4.2 Versions

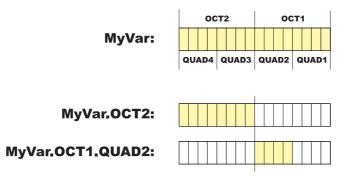

PLEX exists in different versions, PLEX-M and PLEX-C. PLEX-C is used when programming the processor in AXE 10, and since CME 20 is built on the AXE 10 switch technology, PLEX-C is used when developing services here. PLEX-M is used when programming a special part in the AXE 10 system called EMRP, which controls the subscriber stage. PLEX-M is an 8-bit version of PLEX-C, which is a 16 or 32 bit programming language, depending on what processor the target system (exchange) has.

#### PLEX-C

### 4.3 System

The code itself has similarities with Pascal, but the differences are many. The major differences are:

- only one variable type (a group of bits) which can have different properties

- different jump statements

- negative numbers cannot exists

- pointers are in reality circular array indexes and not memory addresses

- it is a real-time language, means that the order of execution is not predictable before execution

- communication between blocks are handled by signals

### 4.3.1 Standard

Many designers are involved when a product is developed, and with new releases, changes in the source code will be made. For that reason design rules exists. The design rules tells the designer how to implement the program so that other designers easily can make changes. When programming PLEX code, one must comply with a "PLEX standard". For a system written in PLEX, five different kinds of documents have to exist and all of them have a common part, an ID sector at the end of the document. This ID sector contains information about the document, e.g. document number, author, responsibilities, version etc. The documents are:

- SPI Source Program Information

- **SPL** Source Parameter List

- **PL** Parameter List

- SS Signal Survey

- SD Signal Description

#### **SPI - Source Program Information**

This document contains the source code. It is here the designer writes or changes the executable statements. It can be PLEX-C code but also ASA assembler code. ASA is used when time critical functions have to be implemented.

The SPI document consists of different sectors. The first is a *declare sector* in which all declarations are stated. The next sector is the *program sector*, which can in itself be two sectors, one for PLEX-C code and one for ASA assembler code. The third is the *data sector*, in which initial values are assigned to some variables declared in the declare sector. Also statements to specify the order of the variables in the data store are here. The last sector is the *ID sector* which is described above.

#### **SPL - Source Parameter List**

This document contains the default parameter values for all data in the PL document (see below).

#### **PL - Parameter List**

The products that Ericsson develops will be released in many different countries and certain data has to be adapted to the local market. This can for example be tone-types, printouts in the local language, charging parameters, etc. These market dependent data should be included in this document to avoid frequent modifications of the source code in SPI.

#### SS - Signal Survey

The signals that a block sends and receives are listed in a Signal Survey document. Each block has its own SS document.

#### **SD - Signal Description**

There is one SD document for each signal. The SD document contains a description of the signal, information about the signal's purpose, type and data. All SD's are stored in a signal-handling library.

All these documents together form a PLEX-C program. A PLEX-C program example (not all documents, only the SPI) is shown here. The program calculates the difference between a received value and a max value (set in the data sector).

```

DOCUMENT PROGEXAMPLE;

DECLARE;

VARIABLE CNUMBER (16) 4 DS;

VARIABLE CNUM 4 DS;

VARIABLE CMAX 4 DS;

END DECLARE;

PROGRAM; PLEX;

ENTER MYSIGNAL WITH CNUM;

! RECIEVE SIGNAL !

CNUMBER = 8 - 31; ! CNUMBER = 65513 (NO NEGATIV NUMBERS) !

! CALL SUBROUTINE SUM !

DO SUM;

SEND YOURSIGNAL WITH CNUMBER; ! SEND SIGNAL !

EXIT;

! SET PROGEXAMPLE IDLE !

END PROGRAM;

PROGRAM SUM; ASA210C; ! ASA SECTOR, SUBPROGRAM !

RS WR1-CNUM; ! STORE CNUM VALUE IN REGI

! STORE CNUM VALUE IN REGISTER WR1 !

RS AR0-CMAX;

! STORE CMAX VALUE IN REGISTER AR0 !

! CALCULATES AR0 - WR1 AND STORE ANSWER IN WR1 !

AR WR1-AR0;

! STORE WR1 VALUE IN CNUMBER VARIABLE !

WS CNUMBER-WR1

END PROGRAM;

DATA;

SIZE OF CMAX = 10;

END DATA;

END DOCUMENT;

ID PROGEXAMPLE TYPE DOCUMENT;

CLA 19055;

REV C;

DAT 99-04-19;

```

DES ERA/LVA/DX MBER; RES ERA/LVA/DC; APP ERA/LVA/DC; END ID;

# 5.1 Description

SDL is the abbreviation for *Specification and Description Language*. It is a high-level, object-oriented and graphical language, which is intended for developing complex, realtime and communication systems. Examples are cellular and DECT phones, exchanges, radio systems, and train-control systems [W1]. A program written in SDL can be presented in two ways, either graphical or textual. The most common way is the graphical because of its benefits (see section 5.3).

# 5.2 History

In 1972 a study group within the telecommunication union CCITT (now called ITU-T) began to research on a specification language that the telecom industry could use. In 1976 SDL got standardized by ITU-T, as standard Z.100. Every fourth year a new version is released. The modifications in summary are [P2]:

- SDL-76 First standardized version. It only had recommendations on how process graph symbols should be drawn.

- SDL-80 The block conception is introduced and the PR-form (textual representation) becomes a part of the language.

- SDL-84 Additional concepts are introduced, among others the concept of abstract data types.

- SDL-88 Only minor changes.

- SDL-92 SDL becomes object-oriented.

• SDL-96 Minor changes, e.g. external procedures

# 5.3 Benefits

The benefits that SDL has compared to other programming languages such as C/C++ and PLEX are many. Some of them are [W1][P2]:

- **Graphical user interface.** The graphical interface makes the software easier to understand, even for a non-technician. One can easy get a clear picture of how the system is built up by different parts, and how they communicate.

- Easy to use. Designing a SDL program is done graphically with help from a tool. The SDL code can then be translated into executable code without any manual "line" coding, as in C++ programming. This makes the development time shorter and increases the quality.

- **Documentation.** Since SDL is graphical, the program itself becomes a document that is easy to read and shows how the system is implemented.

- **Test and maintenance.** The fact that SDL has a rich grammar which describes behaviour, makes it possible to build simulation tools for SDL systems and validate formal characteristic (e.g. to avoid deadlock). This means that defects can be found very early in the development process.

- **Design and implementation independent.** SDL is independent of the design paradigm, i.e. if it is function oriented (PLEX-C) or object oriented (C++). SDL is also independent of the implementation language, which means that SDL code can be compiled to any language one want, e.g. C, java.

# 5.4 Telelogic Tau

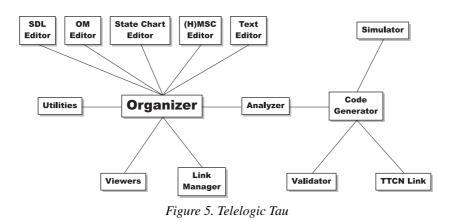

In our work we have used a toolkit for SDL development, and it is the Swedish company *Telelogic AB* that have produced (and now improves) it. The toolkit is called *Telelogic Tau*, hereafter referred to as Tau. Tau is an SDT (SDL Development Tool), and for that reason Tau sometimes are referred to as SDT, i.e. SDT and Tau means the same thing. With Tau it is possible to build SDL applications, test them, simulate live performance, debug SDL programs, make test files etc. Many companies, for example Telia, Siemens Defence, Atlas Copco, Alcatel, Ericsson, IBM, Intel and Nokia use Tau in their development [P2]. Tau is a set of several tools connected to each other as shown in figure 5.

#### Organizer

The Organizer is the central tool in Tau. When starting, the Organizer is appearing. It shows all components in the system and how they are connected. One can compare the Organizer with an advanced file manager.

#### Editors

Tau has several editors for different purposes. The most used editors are the *SDL Editor* and the *MSC Editor*. With these editors SDL and HSDL (High-level SDL) respectively MSC and HMSC (High-level MSC) can be edited. Other editors are *Text Editor*, *State Chart Editor* and *OM Editor*. State Charts show an overview of the states in an SDL program, and OM (Object Model) concerns objects in high-level design.

#### Analyzer / Code Generator

The *Analyzer* checks SDL systems for errors, such as unconnected symbols, undeclared variables, type conflicts, etc., and the *Code Generator* makes executable code. The code can be C code, PLEX-C code, or compiled code ready to run, for instance in the simulator or the validator.

#### Validator / Simulator

With these tools a system can be tested. The difference between them is that in the *Valida-tor* MSC's are compared with the SDL code to see if their flows correspond to each other, and the *Simulator* simulates the program and a test engineer can send in any signal with parameters and check what he gets back. Of course both validation and simulation can be automated.

#### Viewers

The *Type Viewer* shows objects and their inheritance, the *Coverage Viewer* shows how much of the code that was covered by a certain test (with validator or simulator), and the *Cross Reference Viewer* is used to locate definitions and all references to them.

#### Utilities

An example of a utility is the *Preference Manager* where all settings for Tau can be adjusted.

#### Link Manager

This tool handles links between different objects in the system, where objects may be text fragments in text documents or graphical symbols in for example SDL and MSC diagrams.

#### TTCN link

TTCN (Tree and Tabular Combined Notation) is a standardized test language that makes it possible to test the system with same test files in different environments, and the *TTCN link* is what it says, a TTCN link.

# 5.5 SDLtool

Since PLEX-C and SDL does not support the same things (more in section 5.7), Tau has been adapted to fit Ericsson's need for development, and that tool is called *SDLtool*. The differences is that some local tools that help the designer with the differences between SDL and PLEX-C has been added, and some functionality, e.g. object orientation, is removed due to the fact that PLEX-C does not support them. A new code generator has also been added, a PLEX-C generator. It converts SDL code to PLEX-C code, and is further referred to as the PLEX-C generator, or SDL2PLEX. SDLtool is built on Tau, and new versions of Tau also make new versions of SDLtool.

# 5.6 The SDL language

An SDL system consists of several *extended finite state machines* (EFSM) that run in parallel [P5]. The EFSM is an extended concept of the *finite state machine* (FSM). The FSM consists of a set of states with the possibility to receive signals. The signal that is received sets the next state. No variables are allowed and that makes the FSM good for small problems only. Some functions, such as counting, will bring a need of many states. Therefore the FSM concept was extended to the EFSM. In this machine variables are allowed. The EFSM's, or processes, communicate with signals and runs independently.

#### 5.6.1 Components

The following components are embedded in an SDL system [P2]:

- Structure System, block, process, and procedure hierarchy

- **Communication** Signals with optional parameters and routes (channels)

- Behaviour Processes

- Data Abstract data types (ADT)

#### SDL

#### • Inheritance Describing relations and specialization

#### Structure

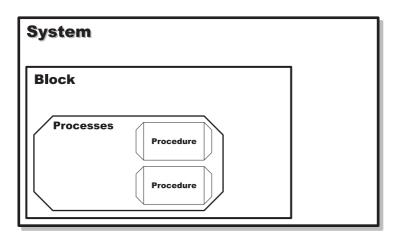

An SDL system is divided into four hierarchical levels (see figure 6).

Figure 6. SDL system

- **Procedures** may be recursively implemented and they can both be local to their process or global, depending on their scope.

- **Processes** in SDL have its own separate memory space and is defined as a nested hierarchical state machine.

- Blocks are a set of processes and other blocks grouped together.

- The system is where all blocks are connected to each other and to the environment.

#### Communication

The communications inside an SDL system, between the processes, are made with signals. They are asynchronous, i.e. the order of their execution cannot in advance be stated. Remote procedure calls can be seen as synchronous signals, i.e. correspond to goto statements or subroutine calls. Both signal types can carry parameters to the receiver. It is not only SDL processes that can send and receive signals but also hardware (called environment in Tau) or non SDL applications. This is for instance necessary when using timers. An SDL process can set timers, and when the timer expires, a timer signal is sent to the process. The timer can also be mapped to an operating system timer or a hardware timer, which makes it possible to simulate time in SDL models, before the target system is available [W2].

The idea of SDL's clear signal interfaces between different parts in a system simplifies large team development and ensures consistency between the parts. But signals and processes cannot be prioritized, priority does not exist in SDL.

#### Behaviour

Processes can be created at system start and at run time. They can also be terminated at any time. More than one instance of a process can exist, and all instances have their own identification number PId, so signals can be sent to special instances of a process.

#### Data

Data can be described in two ways, abstract data types (ADT) and abstract syntax notation one (ASN.1). ASN.1 enables sharing of data between languages. ADT has no specified data structure, instead a set of values, operations and equations are specified. Standard variables are also available, such as integer (numbers without decimals), real (numbers with decimals), boolean (true or false), time, charstring (text), PId (process identification), etc.

Type declarations (the part where the programmer declares which variables he/she will use and what kind of types they are) can be placed any were. It can be either inside the system close to their context, at system level, or even outside the system in packages, which makes it possible to share declarations with other systems.

#### Inheritance

In object oriented languages one of the major benefits is that new objects can be created by adding new or changing properties to existing objects (specialization). This can of course be done in SDL, but since SDL10 is not object oriented (see section 5.7), this is not explained here.

## 5.6.2 The layout of SDL

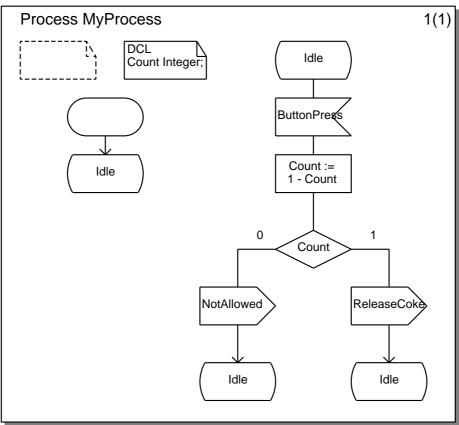

To understand the graphical user interface of SDL and how easy it is to understand, figure 7 shows an example of an SDL process.

Figure 7. SDL Process

The process is "resting" in the Idle state, waiting for the signal ButtonPress to arrive to the process. When the signal arrives, a local variable, Count, is set to a value. In this case it is oscillating between 0 and 1 every time the signal arrives. Then the value that Count holds is checked, if it is 1 the signal ReleaseCoke is sent, otherwise, if Count is 0, the signal NotAllowed is sent. After any of the signals are sent, the process goes to its Idle state.

Where the signals are sent cannot be seen in this figure. It is the overlaying block views that show that, and block views will not be shown here.

# 5.7 SDL10

*SDL10* is an adapted version of the standardized SDL language, made for fitting Ericsson's need. All functionality that PLEX-C gives must also be supported by SDL, and with both limitations and extensions towards SDL, SDL10 fulfils their requirements. Tau supports

SDL, and SDLtool supports SDL10. Differences between PLEX-C and SDL are described in section 6.2.

The extensions are implemented in SDL as directives, i.e. direct commands to the SDL2PLEX compiler. The disadvantage of this is that it will be harder to test the systems behaviour at SDL level. Directives are written as comments in SDL, and begin with a keyword (called directive). The directives can have parameters as well. Examples of extensions are ASA subprograms, external code, ID sector, signal priority and temporary variables.

Limitations are functionality in SDL that are not supported in SDL10. An example of a limitation is the object-oriented concept and thereby also specialization.

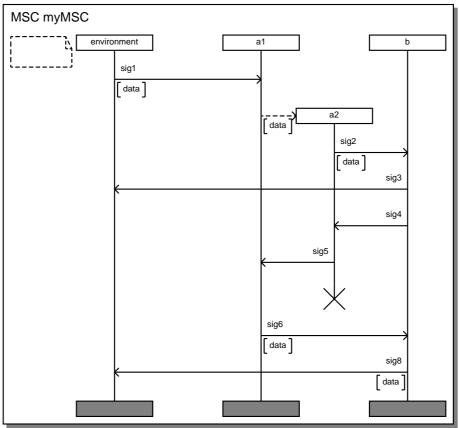

# 5.8 MSC

In real time systems the different processes performs tasks and like all programs they need input data to make decisions (otherwise the developer should know the result of the program execution). A process retrieves data from other processes or components, such as the environment, and it is carried on signals. Signals, or events, must happen in a specified order, e.g. it should not start to ring in a phone before the caller has finished the dialling. An MSC (Message Sequence Chart) shows chronological sequences of messages, or signals, sent between components and their environment. MSC is like SDL standardized by ITU-T, Z.120 [P2].

An MSC is useful for describing the dynamic behaviour of a system. The graphical presentation shows complex behaviours clear and it is easy to understand. Even non-technician people can understand MSC's.

In Tau, test files for SDL systems can be generated from MSC's. An MSC does not describe the complete behaviour of a system though, rather one execution trace. On the other hand several MSC's can describe the system more detailed [P2].

Figure 8. MSC

Figure 8 shows an MSC. The rectangles at the top with text inside are different processes or components in the system. When they are at the top it means that they are already started and are running when the events that this MSC shows begin to happen. The grey boxes at the bottom means that the components not are terminated here and will be running after the events that this MSC shows. The dotted line marks creation of instances during run time in SDL. Process **a2** is created by process **a1**, and then terminated, showed with a large cross. The arrows in an MSC represent events, which is signals in SDL. The text above an arrow is the name of the signal and the text below, inside the brackets are the data sent along with the signal [P2].

SDL

There are both differences and similarities between SDL and PLEX-C. The similarities are the reasons for choosing SDL instead of any other programming language. The differences are the major problems for our work. To have a successful programming language change, we must find solutions for all the problems that the differences bring.

# 6.1 Similarities

#### Realtime

Both PLEX-C and SDL are realtime languages, and use signals to communicate between different parts in the system.

#### Development

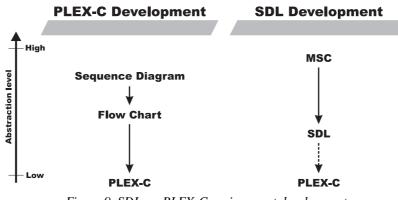

Development in SDL, or actually in the SDL environment, is similar as in the PLEX-C environment. The tools are different of course, but their purpose are the same. Figure 9 shows the corresponding documents between SDL and PLEX-C. Dashed lines represents automatic steps. Note the differences in the abstraction levels.

- First MSC's / Sequence diagrams are produced. They both show interaction between blocks, i.e. signals sent and received within certain functions, but sequence diagrams explains a little bit more than MSC's and have therefore a lower level of abstraction.

- The next step is generation of SDL code respectively flow charts. They both describes what should be done between the signal communication described in the MSC's / sequence diagrams. Since the "what to do" part is implemented with statements in SDL and with explaining sentences in flow charts, there is a difference in abstraction level.

• In the last step PLEX-C code will be generated. In the SDL environment this is automatic, but in the PLEX-C environment this is a manual step and done with help from flow charts.

Figure 9. SDL vs. PLEX-C environment development

# 6.2 Differences

## Variables

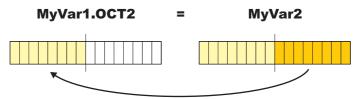

In PLEX-C the variables are a set of bits stored in the memory in different ways. SDL has a numerous of different types, and their scope can be either global or local. A local SDL variable is comparable to a temporary PLEX-C variable. There are also differences between their timer variables (a variable that periodically is increased).

## Typing

SDL is a hard typed language, i.e. assignments and comparisons of two variables must have the exact same type, or must be converted so the types on both sides the equal sign respectively the assign sign are the same. In PLEX-C there is no typing at all. 16 bits structured variables can be assigned 16 bits pure and unstructured variables, even eight bits variables can be both compared with and assigned 16 bits variables' values and vice verca. This is not possible in SDL.

## **Object orientation**

One benefit with SDL is that it is object oriented. This benefit is no argument for changing programming language from PLEX-C to SDL since PLEX-C is not object oriented, and this feature cannot be used.

## System overview

The SDL environment consist of several tools, e.g. SDL editor, MSC editor, Simulator, Analyzator, log window, code generators, etc. which are integrated and connected to each other within an Organizer. The close relationships between the tools makes the system overview clearer than in PLEX-C development. In the PLEX-C environment, similar tools are used in development, but the close integration and connections between them that SDLtool supports does not exist. This is no disadvantage for a programming language

change though, rather a benefit that not affects the difficulties for converting from PLEX-C to SDL.

#### Start/restart, forlopp handling and size alteration

Ericsson has some functionality that handles special cases that can occur in the system. The *start/restart* function is used when the system is started or restarted after a fault has occurred in the system. *Forlopp handling* is a function that kills just that process that has stopped for any reason. The benefit is that all other processes can continue as before. Each process has its own database over connected MS's with data that is relevant for the process. Sometimes the size of these databases needs to be changed and it is the *size alteration* function that handles that. These functions cannot be found in SDL, but PLEX-C has them.

#### Abstraction level

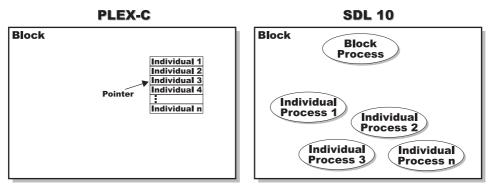

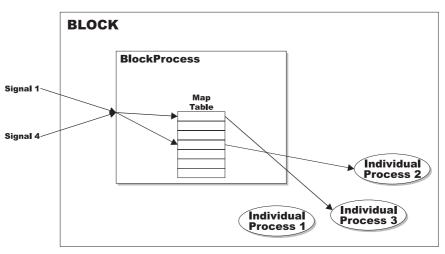

As mentioned before, SDL has a higher abstraction level than PLEX-C. In this case the differences in abstraction level is mostly noticed in the presentation of the source code, i.e. the flow through the program is more obvious in SDL than in PLEX-C. But it is also noticed in the way the different programming languages presents a system in. PLEX-C is not a multitasking programming language (a method to make several programs run parallel), i.e. only one part of the code can be executed at a time and the multitasking has to be considered by the designer, or with other words, the designer decides when his program shall release the processor so other programs can execute. A program in this case is one block. At SDL level, processes (the corresponding to programs) runs parallel, i.e. multitasking. Every block has one *block process* that handles common functionality for the block, and may also have numerous of *individual processes*, and each of them handles a single subscriber in the system (individual). In PLEX-C the subscribers' data are stored in a large database that is constructed like a record in Pascal, or a structure in C. Actually the record, or structure is a large two dimensional matrix were each row corresponds to a certain individual. The individuals are reached with a pointer that says what individual should be handled.

Figure 10. Individuals in PLEX-C and SDL

# 6.3 Conclusions for similarities and differences

The differences cannot be so extensive that it is impossible to convert from PLEX-C to SDL and the similarities must overcome the differences. The realtime similarities are very good and makes it possible to do the language change, but the abstraction level differences makes it hard, actually very hard. The designers have to reassess and attack the problems in a different way.

Previously in this thesis references to a *reverse tool* has been presented, but no deeper explanation about it was provided. The history of the reverse tool's development can be found in section 3.6 and since it still is under development, new versions are released continuously. The tool is developed by Telelogic and integrated inside SDLtool as a menu choice.

Figure 11. The reverse tool within the reverse process

Figure 11 shows where in the reverse engineering process, described by figure 3, the reverse tool is. Dashed lines are work made by the reverse tool and straight lines are manual work. The reverse tool is mostly interested in the compiled source code, and the source

code itself is only used to achieve comments in the code. The tool produces two things, the uncompleted SDL code, and a log that describes what was not converted and has to be done manually.

As described previously, the reverse tool cannot convert all code automatically. There are two reasons for this, first the tool does not support all PLEX-C constructs, for example linked lists, and second some parts are generated by the SDL2PLEX generator and does not need to be implemented in SDL. The second part is recognized as automatic generated code and more about that below.

# 7.1 Block division

When converting blocks with the reverse tool, the percentage PLEX statements converted may vary much. The reason is that the tool does not support all constructs, and in different blocks different constructs are used. Comparing a block's construct with its purpose shows a strong connection, and for that reason blocks can be divided into four categories depending of their purpose. The categories were briefly discussed in section 3.6.6 and also in [I5].

#### Traffic blocks

These blocks handles traffic related jobs, for example handovers and assignments. The percentage of automatic converted statements is high (75% - 95%) (result from [I5] and own experience), since they are the easiest blocks to convert.

#### **Command blocks**

An exchange operator can from a terminal adjust the exchange's behaviour by commands. These commands are handled by *command blocks*. These blocks are, compared to other kinds of blocks, relatively small.

#### Database blocks

These blocks works as databases and stores information, for example about subscribers, cells etc.

#### Message handler blocks

The nodes in an GSM network, i.e. BSC, MSC, BTS, etc., are communicating with standardized messages. *Message handler blocks* converts data retrieved within these messages to the data format used internally in the node.

The reason for traffic blocks being the most successful blocks to convert is that the reverse tool is mostly tested on these kinds of blocks, and for that reason most of the trouble reports to the developer is from converting such blocks.

# 7.2 Reverse tool unsupport

Since the reverse tool is under development, new versions with more support for uncovered constructs will be implemented in the future. The purpose of this section is to show