## Performance Improvements for the Rasterization Pipeline

Jon Hasselgren Department of Computer Science Lund University

LUND INSTITUTE OF TECHNOLOGY Lund University

ISBN 978-91-976939-2-9 ISSN 1404-1219 Dissertation 32, 2009 LU-CS-DISS:2009-3

Department of Computer Science Lund University Box 118 SE-221 00 Lund Sweden

Email: jon@cs.lth.se WWW: http://www.cs.lth.se/home/Jon\_Hasselgren

Typeset using  $\[Mathbb{L}^{*}\]$ EX2 $\[ensuremath{\mathcal{E}}\]$ Printed in Sweden by Tryckeriet i E-huset, Lund, 2009  $\[ensuremath{\mathbb{C}}\]$  2009 Jon Hasselgren

## Abstract

Performance improvements are always needed in computer graphics. Better performance frees up computational resources which can be used to increase the level of realism in the rendered images. Despite a very rapid development of graphics hardware, we are still far from the point where photo-realistic rendering can be done in real time. Therefore, better algorithms must be developed in order to advance the field.

In this thesis, we present several new algorithms targeted for the rasterization pipeline, which is, at the time of writing, the de-facto standard rendering algorithm used in graphics hardware. We focus on three areas in the pipeline. The first is the rasterization step where we present efficient sampling strategies which can improve performance, or enable new algorithms to be implemented. This includes an investigation of very inexpensive, but relatively high quality, sampling schemes, an algorithm for conservative rasterization through area sampling, and an algorithm for efficiently rasterizing multiple views which can be useful for holographic displays, and other multi-view displays.

The second area of focus is on compression algorithms. Compression is frequently used in graphics hardware in order to minimize memory traffic and thereby increase performance. We present efficient algorithms for high dynamic range texture compression, depth buffer compression, and color buffer compression. The inner workings of buffer compression have been kept secret by hardware vendors, and the only available information is available through patents. Therefore, we also present surveys of the prior art in buffer compression.

The final area we focus on is programmable culling. Culling is an old concept in computer graphics, and it is often necessary to include some form of culling to make an algorithm truly efficient. However, current graphics hardware only has a few fixed function culling algorithms implemented. This often makes it impossible, or impractical, to implement culling in new rendering algorithms that rely on graphics hardware. We present a methodology for automatically deriving culling algorithms from shader programs, and we show how this can be used to perform culling both on a pixel level, and on a geometry or vertex level. In both cases, we show that our automatic culling can greatly improve rendering performance for a wide variety of scenes.

## Acknowledgements

First of all I would like to thank my main supervisor Tomas Akenine-Möller for always supporting and encouraging me during this work, and for the many rewarding discussions. I also wish to thank my assistant supervisor Lennart Ohlsson for his support when Tomas was not available.

I would also like to thank my colleagues in the computer graphics group for all great discussions and brainstorming (Petrik Clarberg, Calle Lejdfors, Jacob Munkberg, and Jim Rasmusson), and all the masters students I have worked with during their thesis projects.

The work presented in this thesis was carried out within the Computer Graphics group (LUGG) at the Department of Computer Science, Lund University. It was partly funded by Vetenskapsrådet. Also, thanks to ATI for their fellowship program funding.

Finally, I would like to thank my family and my friends for always being there for me.

## Preface

This thesis summarizes my research on performance improvements for the rasterization pipeline. The following papers are included:

- I. Jon Hasselgren and Tomas Akenine-Möller, "A Family of Inexpensive Sampling Schemes", in *Computer Graphics Forum* 24(4):843–848, 2005.

- II. Jon Hasselgren, Tomas Akenine-Möller and Lennart Ohlsson, "Conservative Rasterization", in *GPU Gems 2*, pages 677–690. Addison-Wesley Professional, 2005.

- III. Jon Hasselgren and Tomas Akenine-Möller, "An Efficient Multi-View Rasterization Architecture", in *Proceedings of EGSR*, pages 61–72, 2006.

- IV. Jacob Munkberg, Petrik Clarberg, Jon Hasselgren and Tomas Akenine-Möller, "High Dynamic Range Texture Compression for Graphics Hardware", in ACM Transactions on Graphics, 25(3):698–706, 2006.

- V. Jon Hasselgren and Tomas Akenine-Möller, "Efficient Depth Buffer Compression", in *Graphics Hardware*, pages 102–110, 2006.

- VI. Jim Rasmusson, Jon Hasselgren and Tomas Akenine-Möller, "Exact and Error-bounded Approximate Color Buffer Compression" and Decompression", in *Graphics Hardware*, pages 41–48, 2007.

- VII. Jon Hasselgren and Tomas Akenine-Möller, "PCU: The Programmable Culling Unit", in *ACM Transactions on Graphics*, 26(3):92, 2007.

- VIII. Jon Hasselgren, Jacob Munkberg and Tomas Akenine-Möller, "Automatic Pre-Tessellation Culling", ACM Transactions on Graphics, 28(2):19, 2009.

The following papers are also published but are not included in this thesis:

- Jon Hasselgren and Tomas Akenine-Möller, "Textured Shadow Volumes", in *Journal of Graphic Tools*, 12(4):59–72, 2007.

- Tomas Akenine-Möller, Jacob Munkberg and Jon Hasselgren, "Stochastic Rasterization using Time-Continuous Triangles", in *Graphics Hardware*, pages 7–16, 2007.

- Jacob Munkberg, Petrik Clarberg, Jon Hasselgren and Tomas Akenine-Möller, "Practical HDR Texture Compression", in *Computer Graphics Forum*, 27(6):1664–1676, 2008.

- Jacob Munkberg, Jon Hasselgren and Tomas Akenine-Möller, "Non-Uniform Fractional Tessellation", in *Graphics Hardware*, pages 41–45, 2008.

- Jacob Ström, Per Wennersten, Jim Rasmusson, Jon Hasselgren, Jacob Munkberg, Petrik Clarberg and Tomas Akenine-Möller, "Floating-Point Buffer Compression in a Unified Codec Architecture", in *Graphics Hardware*, pages 75–84, 2008.

- Henrik Malm, Magnus Oskarsson, Eric Warrant, Petrik Clarberg, Jon Hasselgren, Calle Lejdfors, "Adaptive enhancement and noise reduction in very low light-level video", in *Proceedings of ICCV'07*, pages 1–8, 2007.

# Contents

| 1       | Intro   | duction                              | 1  |

|---------|---------|--------------------------------------|----|

| 2       | The F   | Rasterization Pipeline               | 3  |

|         | 2.1     | Discussion                           | 6  |

| 3       | Raste   | rization                             | 8  |

|         | 3.1     | Sampling                             | 9  |

|         | 3.2     | Multisampling                        | 10 |

|         | 3.3     | Conservative Rasterization           | 11 |

|         | 3.4     | Multi-viewpoint rasterization        | 13 |

| 4       | Comp    | pression                             | 16 |

|         | 4.1     | Texture Compression                  | 17 |

|         | 4.2     | Buffer Compression                   | 19 |

| 5       | Cullin  | ng                                   | 21 |

|         | 5.1     | Programmable Pixel Culling           | 23 |

|         | 5.2     | Programmable Vertex Culling          | 24 |

| 6       | Conc    | lusions and Future Work              | 26 |

| Bibl    | iograpl | hy                                   | 29 |

|         |         |                                      |    |

| Paper I | : A Fa  | mily of Inexpensive Sampling Schemes | 33 |

| 1       | Intro   | luction                              | 35 |

| 2       | Previ   | ous Work                             | 35 |

| 3       | Notat   | ion                                  | 37 |

| 4       | The F   | FLIPTRI Sampling Scheme              | 38 |

| 5       | Samp    | ling patterns                        | 39 |

|         | 5.1     | Initial Pattern Generation           | 39 |

|         | 5.2     | Pattern Ranking and Optimization     | 39 |

| 6       | Resul   | lts                                  | 39 |

|         | 6.1     | Evaluation                           | 40 |

|     | 7      | Conclus     | sion and Future Work                                | 42 |

|-----|--------|-------------|-----------------------------------------------------|----|

|     | Bibli  | ography     |                                                     | 45 |

| Pa  | ner II | : Conse     | rvative Rasterization                               | 47 |

| 1 4 | 1      |             | ction                                               | 49 |

|     | 2      |             | n Definition                                        | 49 |

|     | 3      |             | nservative Algorithms                               | 52 |

|     | -      |             | Clip Space                                          | 52 |

|     |        |             | The First Algorithm                                 | 52 |

|     |        |             | The Second Algorithm                                | 54 |

|     |        | 3.4         | Underestimated Conservative Rasterization           | 57 |

|     | 4      | Robustr     | ness Issues                                         | 57 |

|     | 5      |             | vative Depth                                        | 58 |

|     | 6      |             | and Conclusions                                     | 59 |

|     | Bibli  |             |                                                     | 61 |

|     |        | - 8 · 1 · J |                                                     |    |

| Paj | per Il | I: An E     | fficient Multi-View Rasterization Architecture      | 63 |

|     | 1      | Introduc    | ction                                               | 65 |

|     | 2      | Motivat     | ion                                                 | 66 |

|     | 3      | Backgro     | ound: Multi-View Rasterization                      | 68 |

|     |        | 3.1         | Brute-Force Multi-View Rasterization                | 68 |

|     |        | 3.2         | Multi-View Projection                               | 69 |

|     | 4      | New M       | ulti-View Rendering Algorithms                      | 69 |

|     |        | 4.1         | Scanline-Based Multi-View Traversal                 | 71 |

|     |        | 4.2         | Tiled Multi-View Traversal                          | 72 |

|     |        | 4.3         | Approximate Pixel Shader Evaluation                 | 73 |

|     |        | 4.4         | Accumulative Color Rendering                        | 77 |

|     | 5      | Implem      | entation                                            | 78 |

|     | 6      | Results     |                                                     | 79 |

|     |        | 6.1         | Accumulative Color Rendering                        | 83 |

|     |        | 6.2         | Small triangles                                     | 84 |

|     | 7      | Discuss     | ion                                                 | 84 |

|     | 8      | Conclus     | sion and Future Work                                | 85 |

|     | Bibli  | ography     |                                                     | 87 |

|     |        | - •         |                                                     |    |

| Da. | non T  | 7. TILAL    | Dynamia Danga Taytung Compression for Craphics Hand |    |

#### Paper IV: High Dynamic Range Texture Compression for Graphics Hardware 91

|    | 1       | Introduction |                                                                    |     |

|----|---------|--------------|--------------------------------------------------------------------|-----|

|    | 2       | Related Work |                                                                    |     |

|    | 3       |              | Spaces and Error Measures                                          | 96  |

|    |         | 3.1          | Color Spaces                                                       | 96  |

|    |         | 3.2          | Error Measures                                                     | 97  |

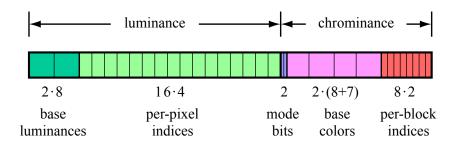

|    | 4       | HDR S        | 3 Texture Compression                                              | 99  |

|    | 5       | New H        | DR Texture Compression Scheme                                      | 100 |

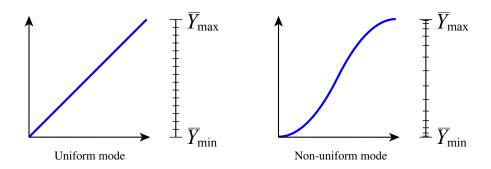

|    |         | 5.1          | Luminance Encoding                                                 | 100 |

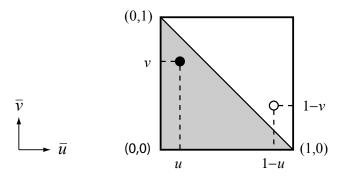

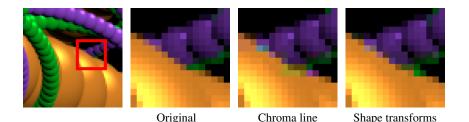

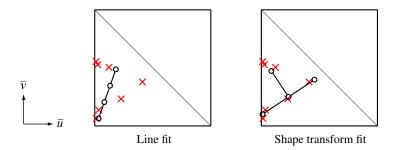

|    |         | 5.2          | Chrominance Line                                                   | 102 |

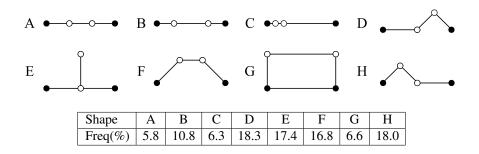

|    |         | 5.3          | Chroma Shape Transforms                                            | 103 |

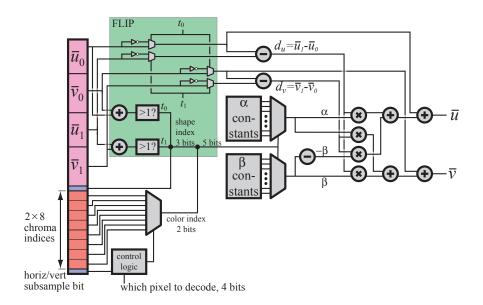

|    | 6       | Hardwa       | are Decompressor                                                   | 105 |

|    | 7       | Results      |                                                                    | 107 |

|    | 8       | Conclu       | sions                                                              | 110 |

|    | Bibli   | ography      | ·                                                                  | 113 |

|    |         |              |                                                                    |     |

| Pa | -       |              | nt Depth Buffer Compression                                        | 117 |

|    | 1       |              | ction                                                              | 119 |

|    | 2       |              | ccture Overview                                                    | 119 |

|    | 3       | -            | Buffer Compression - State of the Art                              | 121 |

|    |         | 3.1          | Fast z-clears                                                      | 121 |

|    |         | 3.2          | Differential Differential Pulse Code Modulation                    | 122 |

|    |         | 3.3          | Anchor encoding                                                    | 123 |

|    |         | 3.4          | Plane Encoding                                                     | 124 |

|    |         | 3.5          | Depth Offset Compression                                           | 125 |

|    | 4       | New Co       | ompression Algorithms                                              | 126 |

|    |         | 4.1          | One plane mode                                                     | 127 |

|    |         | 4.2          | Two plane mode                                                     | 129 |

|    | 5       | Evaluat      | tion                                                               | 132 |

|    | 6       | Conclu       | sions                                                              | 133 |

|    | Bibli   | ography      | ·                                                                  | 135 |

| Da | nor \$7 | Т. Б         | t and Freen hounded Annuarity of                                   |     |

| ra | •       |              | t and Error-bounded Approximate<br>r Compression and Decompression | 137 |

|    | 1       |              | ction                                                              | 139 |

|    | 2       |              | f-the-art Color Buffer Compression                                 | 139 |

|    | -       | 2.1          | Multi-Sampling Compression                                         | 140 |

|    |         | 2.2          | Color Plane Compression                                            | 140 |

|    |         |              |                                                                    |     |

|       | 2.3       | Offset Compression                             |

|-------|-----------|------------------------------------------------|

|       | 2.4       | Entropy Coded Pixel Differences                |

| 3     | A Nev     | w Exact Color Buffer Compression Algorithm 143 |

|       | 3.1       | Reversible Color Transforms                    |

|       | 3.2       | The Algorithm                                  |

| 4     | Error-    | -bounded Approximate Compression               |

|       | 4.1       | The Error Control Mechanisms                   |

|       | 4.2       | A Lossy Algorithm                              |

| 5     | Resul     | ts                                             |

|       | 5.1       | Exact Compression                              |

|       | 5.2       | Approximate Compression                        |

|       | 5.3       | Structural Similarity Index - SSIM             |

| 6     | Concl     | lusions and Future Work                        |

| Bi    | bliograph | ny                                             |

| D     |           |                                                |

| _     |           | CU: The Programmable Culling Unit 157          |

| 1     |           | luction                                        |

| 2     |           | bus Work                                       |

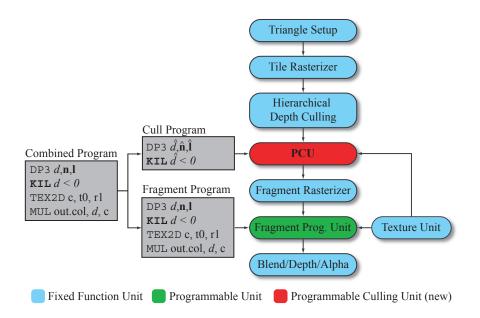

| 3     | -         | ammable Culling Unit Overview                  |

| 4     |           | Interaction                                    |

|       | 4.1       | Driver                                         |

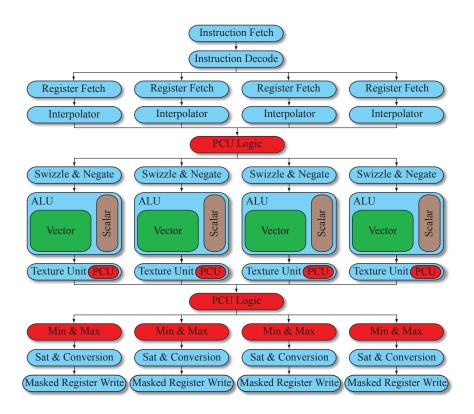

| ~     | 4.2       | Hardware                                       |

| 5     | -         | mentation - Combined Shader Unit               |

| 6     |           | ts                                             |

| -     | 6.1       | Small Triangles                                |

| 7     |           | Ission                                         |

| 8     |           | lusion                                         |

| А     |           | ral Arithmetic Instruction Set                 |

|       | A.1       | Arithmetic and Conditional Instructions        |

|       | A.2       | N-Dimensional Texture Lookups                  |

| р.    | A.3       | Cube Map Lookups                               |

| Bı    | bliograph | ny 181                                         |

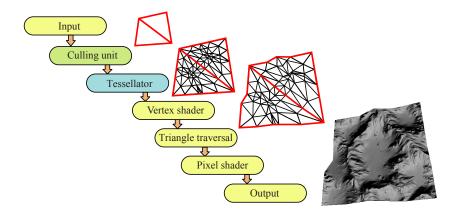

| Paper | · VIII: A | utomatic Pre-Tessellation Culling 183          |

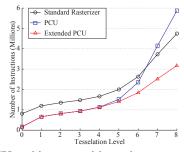

| 1     |           | luction                                        |

| 2     |           | llation Culling                                |

|       | 2.1       | Overview                                       |

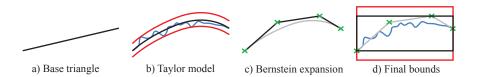

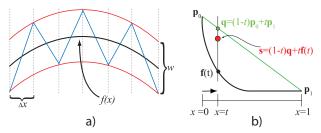

|       | 2.2     | Taylor Arithmetic         188   |

|-------|---------|---------------------------------|

|       | 2.3     | Tight Polynomial Bounds 190     |

|       | 2.4     | Program Analysis and Generation |

|       | 2.5     | Selective Execution             |

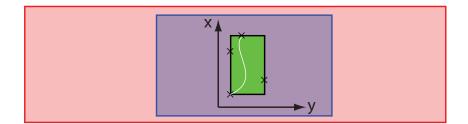

|       | 2.6     | Culling 195                     |

| 3     | Implem  | entation                        |

| 4     | Results |                                 |

| 5     | Conclus | sion and Future Work            |

| Bibli | ography |                                 |

## **1** Introduction

Computer graphics is the science of generating, or *rendering*, images on a computer. In essence, a screen has a limited number of picture elements, or *pixels*, which can be set to any given color, and a graphics algorithm is merely a way to determine which color to display at each pixel. Even though we may not think about it, computer graphics has become part of our everyday life. The most evident use is in computer games and entertainment, but it is also heavily used for special effects in the movies we watch, as well as in the graphic overlays on news and sports TV-broadcasts. Another example of widespread use is mobile phones and portable music and video players. In addition, computer graphics is used to visualize measurements from medical equipment in order to help doctors make the right diagnosis, for example.

A subfield of computer graphics that has been given particular attention is that of three-dimensional graphics. Here, a two-dimensional image is rendered from a three-dimensional model of a virtual scene or world, at a given viewpoint. Such scene models are typically constructed from several objects, where each object is built from triangles that approximate the object's actual surface as shown in Figure 1. The triangles are given material properties that describe how light interacts with the surface, and the task of the rendering algorithm is to determine how light is transferred throughout the scene. The algorithm follows the light from a virtual light source, such as the sun, and registers each surface the light hits before it reaches the viewpoint, thereby giving color to a certain pixel. This is called the light transport problem, and it turns out to be a very complex problem to solve.

The complexity of the light transport problem has divided three-dimensional computer graphics into two branches: *photo-realistic* and *real-time* rendering. Photorealistic rendering focuses on image quality and spends a lot of resources on solving the light transport problem accurately. The rendering algorithms are often

Figure 1: *Left:* A three-dimensional model is constructed from vertices connected to form triangles. *Middle:* When the triangles are rendered, the surface of the model appears. *Right:* Finally, the triangles are given material properties in order to create a more realistic image. These images are based on a free model from www.artist-3d.com.

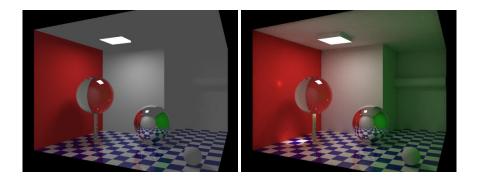

Figure 2: *Left:* An image rendered with a simple light model, not including any indirect lighting. *Right:* The same image rendered with a physically based lighting model. Note that a great deal of the light in this scene actually comes from indirect lighting. As a result, the rendered image to the right looks more realistic, and it also makes it easier to perceive the depth and shape of the scene.

based on physics, and simulate how light interacts in the real world. They capture effects such as indirect lighting, which occurs when light bounce off several surfaces before reaching the eye. Although this may sound like a very subtle effect, it contributes greatly to the perceived realism, as can be seen in the images in Figure 2. In an ideal world, photo-realistic rendering would be used for all purposes, but due to its complexity, it may take a single computer minutes, hours, or even days to render a single image. Photo-realistic rendering is therefore used primarily in the film industry, where a film is rendered during the course of months on big clusters of computers.

The most typical example of the other subfield, real-time graphics, is games, which have two requirements that make accurate photo-realism impractical. First, the player is able to interact with the virtual world as the game is played, so we cannot precompute a movie clip. Second, the images must be rendered in a high enough pace so they are perceived as a fluid animation rather than separate images. This typically requires around 60-100 images to be rendered each second. Therefore, rendering performance always comes first in real-time graphics and quality comes second. The rendering quality is made as high as possible without breaking the performance requirements.

Real-time graphics has received enormous attention during the last few years, and with the introduction of dedicated graphics hardware, performance has increased thousandfold in the last decade. Each time computational power is increased, the extra performance is used to improve image quality. However, consumers quickly grow accustomed to that level of image quality, and we once again need to improve performance in order to improve quality. This is a seemingly never ending cycle, where we continue to improve on graphics performance with the long term goal of bridging the gap between photo-realistic and real-time graphics. There is a general

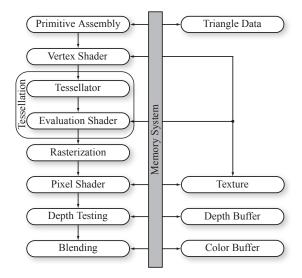

Figure 3: Schematic overview of a modern rasterization pipeline, such as the ones found in current GPUs. The boxes on the left side show which operations are performed in order to render a triangle. As can be seen in the illustration, some of these functional units access storage buffers through the memory system.

yearly performance growth that comes from better manufacturing technology of the hardware silicon. However, this growth alone will not be enough to reach photo-realistic quality in a foreseeable future, for complex scenes. In order to reach that goal, we need to improve on current real-time rendering algorithms, and that is the focus of this thesis.

In this thesis, we propose optimizations and improvements for the rasterization algorithm, which is, at the time of writing, by far the most popular rendering algorithm for real-time graphics. The improvements aim to increase performance with no, or very little, visual loss in image quality. The primary focus is graphics hardware, but our algorithms can also be useful for software rasterization frameworks.

### 2 The Rasterization Pipeline

Today, rasterization is the de-facto rendering algorithm used for real-time graphics applications, e.g., games, but it is also frequently used in high-quality rendering in the feature film industry. Rasterization is a very simple algorithm that can be parallelized very efficiently, and this has made it a perfect candidate for hardware implementation, which has in turn greatly contributed to its popularity. Another desirable feature of the rasterization algorithm is that triangles are processed one at a time, independently of each other. Therefore, scene data can be streamed in from removable media (such as, for example, a hard drive) and need not be stored in memory. This is particularly important in high-quality film rendering, where scenes often are very complex.

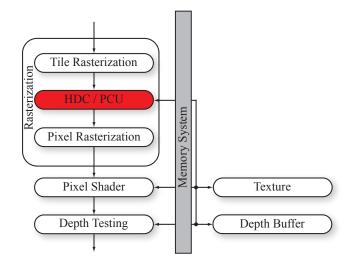

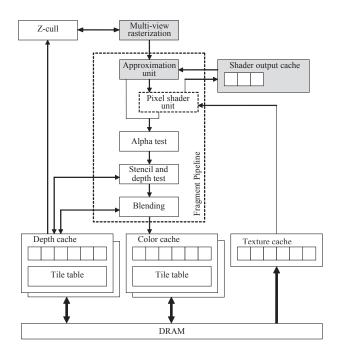

Figure 3 shows a schematic overview of a modern rasterization pipeline, as implemented by most modern graphics hardware architectures. The left part of the figure shows the functional units a triangle pass through in order to be rendered. Some of the functional units access external memory buffers through the memory system, also shown in the figure. A memory access is typically an expensive operation [34] when compared to computations or logic operations, and therefore it is important to minimize the memory traffic as much as possible.

**Primitive Assembly** In the first step, the primitive assembly, a triangle is created by fetching the three corresponding *vertices* from memory. A vertex is specified by its *attributes*, which are typically position, normal, color, and texture coordinates. However, due to the programmability of modern *GPUs* (graphics processing units), the programmer is free to specify any attributes she or he like. In programming terms, one could say that the attributes can be seen as function parameters sent from the CPU to the GPU.

**Vertex Shader** After primitive assembly, the vertices of a triangle are sent to the vertex shader unit [24] (also known as the vertex program unit). This unit is essentially a microprocessor that executes a vertex shader program for all vertices of the triangle. The vertex shader program is written by the application programmer and can be customized to implement visual effects such as skinning, cloth simulation, and collision detection. The only strict constraint on the vertex program is that it must compute the (unprojected) screen position of each vertex of the triangle. However, the vertex program can also be used to compute additional vertex attributes. If that is the case, the attributes will continue down the pipeline, and can be used in the later pixel shader unit.

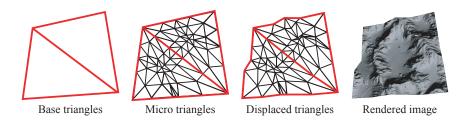

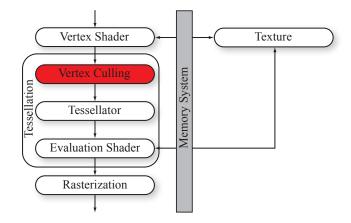

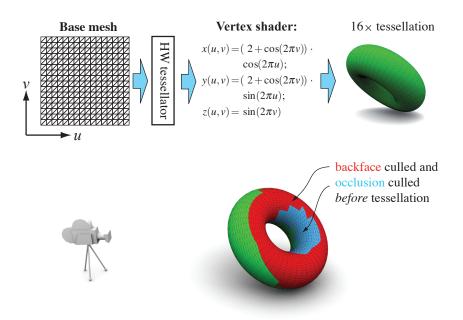

**Tessellation** Tessellation is a recent addition to the graphics hardware rasterization pipeline [13, 14, 46], although it has been used in software-based high-quality rasterizers [9] for a very long time. The tessellator takes a *base triangle*, which is simply the triangle we are currently rendering, and subdivides it into a number of smaller *micro triangles* as shown in Figure 4. The tessellator then executes an *evaluation shader* (sometimes also called a domain shader), which is very similar to the vertex shader in that it is used to alter the position of the newly created vertices. A typical application of tessellation is shown in Figure 4. Two input triangles are tessellated, and a height map is used to displace the position of the new vertices, thus creating a landscape.

Figure 4: When tessellation is enabled, each base triangle is subdivided and several new micro triangles are created. The evaluation shader then alters the position of all the vertices which displaces the newly created triangles, and finally the triangles are rasterized. In this example, a detailed landscape is created from only two input triangles

**Rasterization** Once the vertices' screen space positions have been determined, the triangle is processed in the rasterization unit [26, 33, 35] which identifies the pixels it overlaps. When an overlapping pixel is identified, a *fragment* is generated. A fragment is essentially a container for all data needed through the pipeline in order to compute the final color of a point in the scene. The rasterizer computes fragment attributes by interpolating the corresponding attributes of the three vertices, and sends the fragment further down the pipeline. It should be noted that the rasterization unit acts as a data amplifier as it takes triangles as input and outputs fragments. Typically, a triangle covers more than one pixel thereby generating several fragments, and in the extreme case a single triangle may cover the entire screen.

**Pixel Shader** This unit is also sometimes referred to as the fragment shader or fragment program unit, as it operates on fragments rather than pixels. However, we will refer to it as the pixel shader in the remainder of this text since this is most commonly used. Like the vertex shader unit, this is a microprocessor that executes a user-defined program for every fragment which is generated in the rasterization step. The pixel shader program's primary task is to compute the final color of each fragment as they are drawn to the screen, and it will thereby affect the visual appearance of the object. Some examples of effects that can be implemented in a pixel shading program are lighting models, shadowing, reflection, volumetric lighting effects and custom clipping. In order to render visually rich images, the pixel shader algorithms often need to access texture maps containing surface structures, reflection parameters, and similar data. The texture maps are stored as images in external memory, and therefore the pixel shader unit is one of the main consumers of memory bus bandwidth.

The vertex and pixel shader units are very similar in the way they operate. A vertex or a fragment can be treated equally as they are both defined by a set of attributes. This has led to the *unified shader* unit which, although it still operates as a separate

vertex and pixel shader from the application programmer's point of view, uses the same physical hardware resource to execute both vertex and pixel shaders. This approach uses hardware resources more efficiently, and also have the benefit that it makes load balancing easier. If a scene has more vertices than fragments the unified shader unit will spend more of its time executing vertex shader programs, while in a system with separate shader units, the pixel shader unit would be idle, waiting for the results from the vertex shader unit.

**Depth Test and Blending** Once the fragment has passed the pixel shader unit, its final color and depth have been computed by the pixel shader program. Before the pixel is colored, a depth test [16, 45] is performed to ensure that occluded triangles never are drawn on top of, or bleed through, the triangles that occlude them. This test requires a depth buffer, which is a memory buffer where the depth of each pixel is stored. Whenever a fragment comes to the depth test, the fragment depth is compared to the depth in the depth buffer. If the fragment depth is greater than, or further away from the viewer than the value stored in the depth buffer then the fragment is discarded since it is occluded by something. On the other hand, if the fragment depth is less than (that is, closer to) the viewer than the value stored in the depth buffer, the value in the depth buffer is updated with the depth of the current fragment and the fragment color written to the color buffer in the following blending stage. As the depth test relies on memory accesses, it also consumes a relatively high amount of bandwidth. It should be noted that most graphics hardware allows the exact behavior of the depth test to be configured to allow a wide variety of algorithms to be implemented. However, the "less than" test described here is by far the most commonly used.

Finally, fragments that pass the depth test are written to the color buffer. Instead of simply overwriting the previous color, the application programmer may configure the color blending [4] unit to mix the fragment color with the color previously stored in the color buffer. The primary use of this unit is to render transparent triangles, which is used, for instance, when rendering transparent objects or particle systems. From a memory perspective, blending is very similar to depth testing as both are read-modify-write operations. These steps therefore consume roughly equal amounts of memory bandwidth. However, there are some exceptions to that rule as high dynamic range rendering [37] increases color bandwidth, and shadow rendering algorithms typically rely heavily on depth buffer bandwidth.

#### 2.1 Discussion

Recent developments of graphics hardware have introduced more and more programmable steps into the pipeline, and therefore the graphics cards are starting to look more and more like many-core systems. However, as the rasterization pipeline is a fundamental part of the hardware design, only algorithms that fit into this model can be efficiently implemented. A rather different approach is taken by Intel with their currently unreleased product Larrabee [40], which is a pure many-core processor on which rendering algorithms will be implemented in software with some fixed-function hardware for special case operations such as texture filtering. This has the advantage that rasterization software can continually be improved and customized as new algorithms or optimizations emerge, and it also allows automatic load balancing since there are very little hardware resources allocated for fixed functionality. Whether or not this new product will prove efficient enough despite its programmability remains to be seen. However, there is an apparent convergence between many-core systems and graphics hardware. This makes the algorithms presented in this thesis more attractive as many of them can be implemented entirely in software in a very near future.

So far, we have focused on the desirable features of the rasterization algorithm. However, as previously mentioned, rasterization is really a brute force algorithm. Although it is perhaps this aspect that has made it such a good candidate for hardware implementation, it does not mean that a naive implementation will perform well. Many improvements and optimizations have already been adopted by modern graphics hardware. They focus primarily on reducing computational complexity and memory bandwidth usage. Reducing computational complexity is a pretty straightforward optimization. With a given hardware budget there is only so many computational units you can realize, and therefore you will be bound by some theoretical computational throughput, typically measured in FLOPS (floating point operations per second). If you can reformulate your algorithms to use fewer computations, you gain performance. An example is tiled rasterization [27] where you first test if a *tile*, which is a block of for example  $8 \times 8$  pixels, overlaps the triangle being rasterized. If the tile overlaps the triangle, you need perform an overlap test for each of the 64 pixels, but if it does not overlap you can proceed to the next tile. Since it is less expensive to test if a tile overlaps a triangle than it is to test 64 pixels, you will gain computational performance on average. Another example is to optimize the pixel shader program. Since each instruction in the pixel shader program takes some time to execute, we can very easily gain performance if we can remove instructions or substitute complex instructions for simpler alternatives.

The other target of optimizations is to reduce memory bandwidth usage and this is typically done by improving coherency in memory lookups, by using caches more efficiently, and by compressing memory contents. The general trend of computer hardware is that computational throughput grows at a much faster rate than memory bandwidth [34]. Fortunately, graphics-specialized hardware is much more forgiving than normal processors in this regard since wider memory buses can be used more efficiently, and memory latency can be hidden by processing several pixels in parallel. However, memory throughput is still a great problem which has received much attention in graphics hardware based research.

This thesis covers several novel algorithms targeted for the rasterization pipeline. The focus is mainly on performance improvements both targeting computational complexity and memory bandwidth. We also try to keep modifications to the rasterization pipeline as small as possible in order to make our algorithms easy to implement in existing hardware solutions. With the recent advance of more

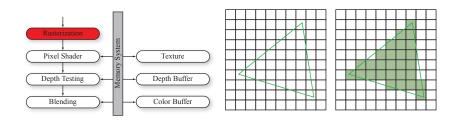

Figure 5: *Left:* Modifications to the rasterization algorithms focus on that particular unit. However, they can also indirectly affect units further down the pipeline. *Right:* Rasterization finds all pixels that overlaps a given triangle. For each such pixel, the rasterizer generates a fragment which contains all data necessary to process that pixel, and sends the fragment further down the pipeline.

programmable hardware, we believe that the algorithms are of practical importance and could be implemented on next generation graphics cards with good results. The algorithms focus mainly on three areas: rasterization, compression, and culling

## **3** Rasterization

As previously mentioned, rasterization determines which pixels overlap a triangle, as shown in the right part of Figure 5. In the simplest form of rasterization, one sample point is chosen to represent each pixel. Determining if a pixel overlaps the triangle or not is done by testing if the sample point lies inside the triangle. This test can be done using *edge functions* [35]. If a pixel overlaps the triangle, a fragment is generated by interpolating all vertex attributes to compute their values at the sample point. The fragment is then passed down the pipeline as shown to the left in Figure 5. It should be noted that changes to the rasterizer may change the data structure of a fragment. This may lead to indirect changes in the fragment processing parts of the pipeline.

In a naive implementation, rasterization would perform the overlap test for all pixels on the screen each time a triangle is rendered. This is not efficient, and consequently many algorithms limit the number of pixels visited either by using some overestimation of the triangle, such as for example its bounding box, or by starting from a pixel overlapping the triangle and visiting all neighboring pixels that also overlap the triangle. Some algorithms, such as recursive descent, work by starting with the whole screen as an overestimation of the pixels the triangle overlaps. The screen is then recursively subdivided into smaller and smaller boxes until a box is not overlapping the triangle, or the box is the same size as a pixel.

Traditionally, the rasterization step is preceded by a clipping [32] and projection step in order to clip the triangle by the view frustum and then project the clipped

Figure 6: The right box is rendered with a single sample per pixel and the right box is rendered using supersampling and 64 samples per pixel.

triangle on the screen. However, clipping algorithms are complex to realize in hardware, and therefore a popular alternative is to use homogeneous rasterization algorithms [26, 33] which directly rasterize the unprojected triangle.

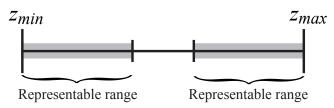

#### 3.1 Sampling

The sampling process is the core of any rasterization algorithm, and just like any other sampling process it is subject to aliasing if the sampling frequency is not high enough. Unfortunately, models built from triangles will have discrete silhouette edges, which have infinite frequency content, so we can never avoid aliasing completely with point sampling strategies. However, by using a high enough sampling rate, we can create a result that is more or less visually indistinguishable from the correct image. To do that, we over-sample the image by using more samples than pixels in the final image. The image is then reconstructed through *filtering* where the color of each pixel is computed as a weighted sum of the colors of the samples within the filter kernel. This is called *supersampling* [41], and the effect is illustrated in Figure 6. High-quality rendering typically use complex filter kernels that covers more than one pixel, such as Gaussian filters. In real-time rendering however, it is still very common to use simple box filters where the color of a pixel is computed as the average of the samples in that pixel.

A disadvantage of supersampling is that it requires huge amounts of pixel processing power. Processing n samples per pixel results in n times more computations in the fragment processing part of the pipeline. Memory bandwidth is also greatly increased, although caches will make the increase slightly sub-linear. An alternative sampling approach that eases this burden is *multisampling*. It is based on the assumption that the majority of the high-frequency content in an image comes from geometry (i.e., triangle edges) and not from shading. With that in mind, several sampling points can be used to determine if a pixel lies within a triangle,

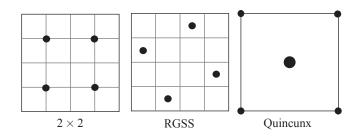

Figure 7: Sample placement is important for visual quality. The RGSS pattern is for instance known to give higher visual quality than the  $2 \times 2$  pattern. Another trick to increase quality is to share samples between pixels. In the Quincunx pattern, the corner samples can be shared by four pixels. Therefore, the cost is two samples per pixel rather than five as one might think.

but the pixel shader program only needs to be evaluated in a single point. The color computed by the pixel shader can then be propagated to all samples that were determined to overlap the triangle. The effect of multisampling is that pixels completely within one triangle will effectively only use a single sample while pixels on triangle edges will get samples from multiple triangles thus smoothing the edge. From a computational and memory bandwidth standpoint, the only difference between multisampling and supersamling is that the pixel shader program is executed only once per pixel for multisampling. However, this is a huge advantage as the pixel shader program contains all texture lookups, which is often the main consumer of memory bandwidth.

In the following, we describe three papers on rasterization (Papers I-III). Although they cover very different areas, they can all be seen as different strategies for sampling tailored for their respective contexts.

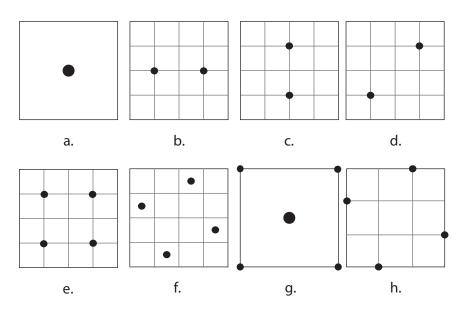

#### 3.2 Multisampling

Even though multisampling helps reduce the most costly part of the supersampling algorithm, it is still a very costly process as rasterization, depth testing, and blending stages must process many more samples. Therefore, it is important to place the sample points strategically to achieve the highest possible visual quality with as few samples as possible. For instance, the RGSS (rotated grid super sampling) [41] pattern shown in Figure 7 has long been known to produce higher quality images than the naive  $2 \times 2$  pattern, also shown in that figure.

The reason why some patterns are visually more appealing than others have been investigated by Naiman [31], who studied how the human eye perceives aliasing of edges at different orientations. Perhaps not entirely surprisingly, it turns out that humans are considerably more sensitive to aliasing of near horizontal and vertical

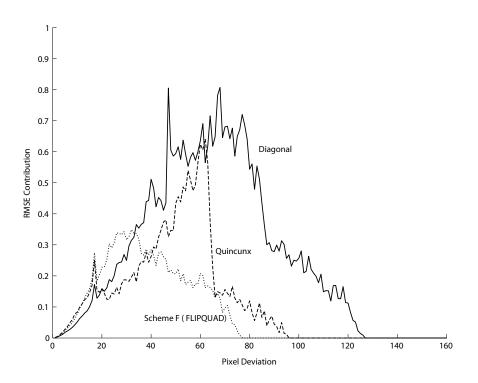

edges. In between those extremities the sensitivity was relatively low with a peak around 45 degrees. The result of Nainan's study motivates why the  $2 \times 2$  pattern from Figure 7 is considered a bad sampling pattern. For near-horizontal or vertical edges, two sample points will trigger at almost the same time, and therefore neighboring pixels will go from being completely outside a triangle to having two sample points inside the triangle. Since RGSS is a rotated version of the  $2 \times 2$ pattern this effect will happen at edge orientations where we have considerably lower visual sensitivity, and this explains why RGSS is a better pattern in practice. Laine and Aila [23] have later quantified sample quality by using an error metric based on the results of Naiman's studies. It should be noted that this quality metric goes in contrast to other sample placement strategies used in high quality rendering [21, 41], which primarily focuses on reducing the variance of a sampled signal. However, it is our belief that it is well suited for real-time rendering as we can only afford very few samples, in which case reducing the perceptual aspects will be more important than variance reduction. Furthermore, the edge studies of Naiman goes hand in hand with the multisampling concept as it exclusively focuses on reducing edge aliasing.

Besides sample placement, sample sharing is also a technique that can be used to improve quality. The Quincunx pattern [10] in Figure 7 is a typical example of sample sharing. When this pattern is replicated, the corner samples will share the exact same positions for neighboring pixels and can therefore be reused.

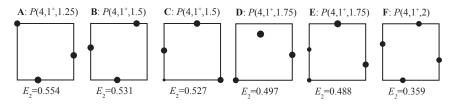

In Paper I, we explore a family of very inexpensive sampling patterns that use between 1.25 and 2 samples per pixel, and present the configurations that will perform best according to the error metric defined by Laine and Aila. We consider sampling patterns that are mirrored horizontally or vertically each time we move one pixel in the horizontal and vertical direction, respectively. Such patterns can share all sample points in pixel corners between four pixels, and all sample points on pixel edges can be shared by two pixels. We performed an exhaustive search of the possible configurations and manually selected the ones that we believed to work well according to Naiman's findings. We then ran an optimization process based on Laine and Aila's error metric to compute final positions and filter weights for the samples. The optimization process is not exhaustive, which means that the presented patterns may not be optimal. However, they perform well relative to their cost as we show in our evaluation, and we believe that these patterns could be very useful for low end-graphics, e.g., for use in mobile devices.

#### 3.3 Conservative Rasterization

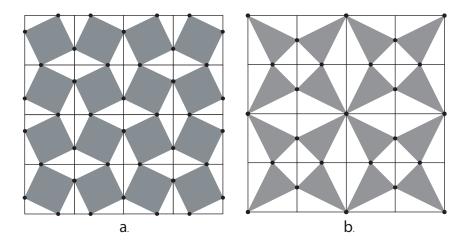

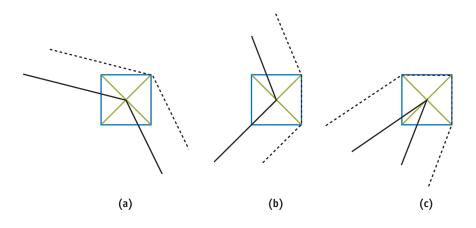

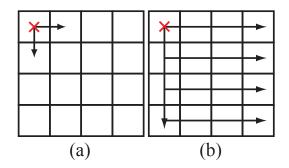

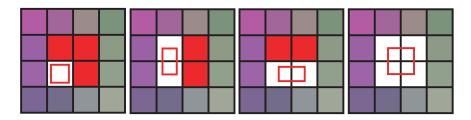

Conservative rasterization can be seen as a special case of sampling. Normally when we rasterize, we only want each sample point to belong to a single triangle, and therefore normal rasterization algorithms have consistent rules to assign sample points that lie on triangle borders to one of the neighboring triangles. All this is necessary to avoid flickering in edges where two triangles meet. Conservative rasterization, however, considers the whole *pixel region* as the sampling

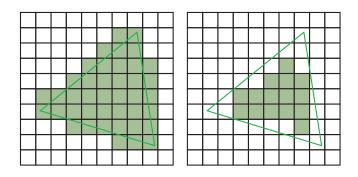

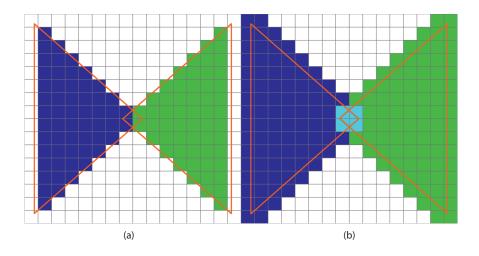

Figure 8: Two forms of conservative rasterization. Overestimated rasterization, shown to the left, visits all pixels that partly overlap the triangle. Underestimated rasterization, shown to the right, visits only the pixels that lie completely within the triangle.

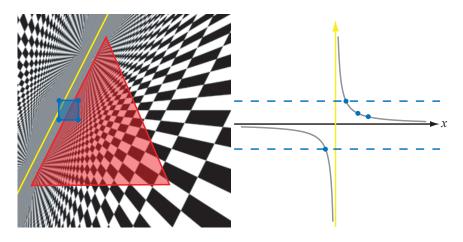

area. As shown in Figure 8, there are two types of conservative rasterization. An overestimating variant that visits all pixels regions touched by the triangle, and an underestimating variant that only visits pixel regions completely within the triangle. In this thesis, we focus primarily on the overestimated variant since it is most practically useful.

Although conservative rasterization has little value for normal rendering, it has the desirable feature that we can accurately detect and handle overlapping polygons. This is particularly important in advanced shadowing algorithms [5, 42], culling algorithms [25], and collision detection algorithms [15, 30]. Since the utility of conservative rasterization has increased, Akenine-Möller and Aila [2] proposed simple extensions to the rasterization unit to support conservative rasterization. However, so far no graphics hardware vendors have thought this feature important enough to implement in hardware. Therefore many algorithms have had to rely on normal rasterization, thereby making it impossible to guarantee their correctness.

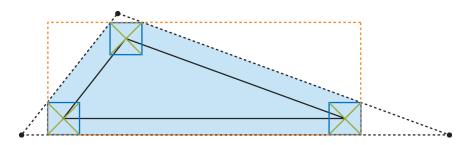

In Paper II, we present two novel algorithms for conservative rasterization. They are designed to work on existing graphics hardware, and can be implemented entirely in vertex and pixel shader programs. The first algorithm was inspired by Akenine-Möller and Aila's algorithm, but modified to fit into the current graphics pipeline. In the vertex shader, we extend the vertices of each triangle so it overlaps the sample point of at least all the pixels that conservative rasterization would traverse. The extended triangle may overlap more pixels than is needed since the shape traversed for overestimated rasterization is not necessarily triangular. We discard the fragments generated for these excessive pixels by using an inexpensive test that is implemented in the pixel shader program. This algorithm has the advantage that it does not increase the vertex or triangle count of the rendered scene. However, for sliver triangles, a large amount of excessive fragments may be generated only to be discarded in the pixel shader program. It can therefore put a

heavy load on the rasterization and fragment processing part of the pipeline. Our evaluation suggests that lower end hardware favors this algorithm. However, this depends on rendering resolution and how the hardware is load balanced for vertex and fragment processing, respectively.

For the second algorithm, we use a different approach and directly generate polygons that cover the centroid sample points of all the pixels that would be traversed by a conservative rasterizer. Since graphics hardware can typically only render triangles, we supply polygons in form of pre-tessellated triangles, where every triangle vertex is duplicated three times. The vertex shader program can then compute the polygons simply by moving the vertices into place. This algorithm has the advantage of generating no unnecessary fragments during rasterization, and therefore do not require a fragment program at all. However, it puts a greater strain on the vertex processing part of the pipeline, since three times as many vertices must be processed. Our evaluation showed that this algorithm is likely to perform better on high-end and modern hardware. Furthermore, the recent addition of geometry programs have made it possible to execute the full algorithm on graphics hardware, without having to send duplicated geometry from the CPU. However, even though at least one recent project [42] has adopted this algorithm with that modification, there are, as of this date, no concrete numbers on how much performance improvement one can expect from using geometry programs.

#### 3.4 Multi-viewpoint rasterization

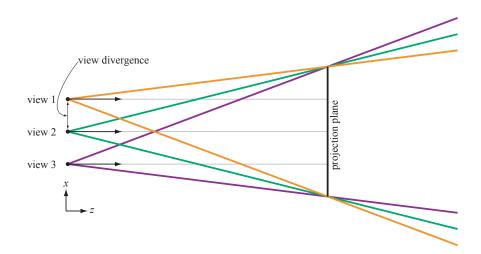

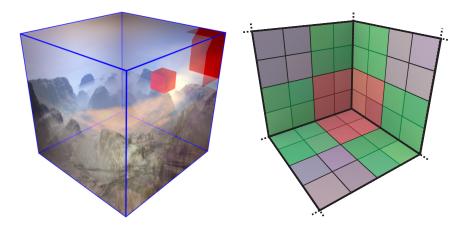

Our final contribution to the family of rasterization algorithms is in the field of multi-viewpoint rasterization. The most simple form of multi-viewpoint rendering is stereoscopic rendering. Our brain uses the images of both eyes as an important cue to perceive depth in a scene, and therefore it is only natural to render one view for each eye as shown in Figure 9. The viewpoints in the virtual scene should be separated by approximately the distance between the viewer's eyes. Taking the concept of stereoscopic rendering one step further, there are multi-viewpoint displays which show different images from different viewing directions [12, 20] without the need of peripheral equipment such as glasses. We do not only get a stereoscopic effect from our eyes seeing different images, but can also move the head to see the scene from different angles. The screen goes from being a flat surface to being a window into a virtual three-dimensional world.

The technology for multi-view displays exists already today. However, a great problem that remains is how to efficiently render multiple views. The naive approach is to render one view at a time, but this causes performance to scale linearly with the number of views. For high-quality multi-view images, we may need between 32 and 64 views, translating to a performance loss of  $32 - 64 \times$ . However, as can be seen in Figure 9, there is a lot of coherence between multi-view images, as the different views look very similar. This coherency can be exploited in the rendering algorithm in order to improve performance. Although there has been some research on this topic [1, 36, 43], there has been very few sugges-

Right Eye

Left Eye

Figure 9: A cross-eyes stereoscopic photography of an exhibition car. Note that the two images look very similar, which indicates that they are strongly correlated. An important key to efficient multi-view rendering is to use exploit this coherency in order to improve performance. Original image from Wikimedia Commons.

tions that could be implemented in a standard rasterization pipeline without large changes. One exception is the research of Halle [17], who presents an algorithm for multi-viewpoint rasterization using existing graphics hardware. Unfortunately, since current hardware is not well suited for multi-viewpoint rasterization, this algorithm works best when rendering a very large number of views. Due to the lack of efficient algorithms suited for a moderate or low number of views, the most used solution at this time is to use the naive approach and render one view at a time, resulting in a big performance reduction.

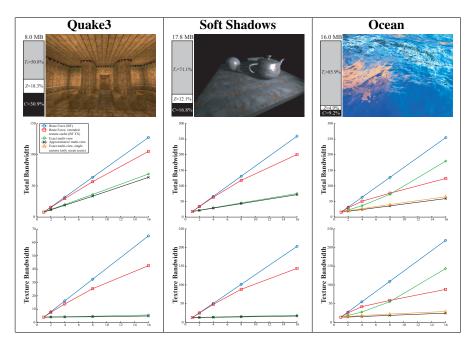

In Paper III, we present a novel multi-viewpoint rasterization algorithm that can reduce both memory bandwidth usage and computational complexity. Furthermore, the algorithm is based on the current rasterization pipeline, and we therefore believe that it could be adopted with relatively modest changes in hardware. The algorithm exploits the coherency in multi-view images, and is based on the observation that a specific point on a specific triangle is likely to result in the same texture lookups and computations for all viewpoints. This assumption holds true for all surfaces with materials which are view-independent, and gracefully degrades the more view-dependent terms are added to the material. A wrinkled mirroring surface, such as the ocean scene presented in our results, is more or less a worst case scenario since it has very high frequency content which is completely viewdependent.

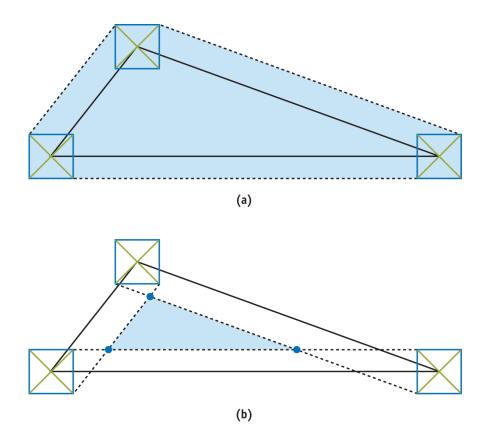

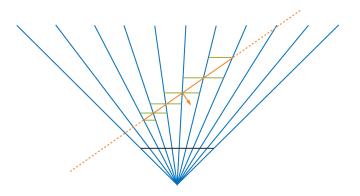

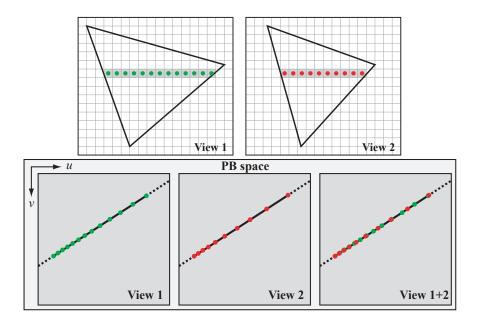

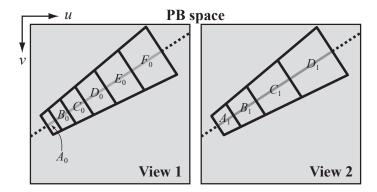

Given our assumption, it makes sense to process one fragment of one triangle, render that fragment to all views, and then continue. This is, however, hard to implement in practice, since the triangle is projected differently for different view-

points, which could lead to cracks or overdraw in some of the views. Instead, we rasterize the triangle from all viewpoints in parallel, and sort the rasterization order so that we always pick the view whose next fragment lies closest (on the surface of the triangle) to the previously processed fragment. This means that we will not process the exact same point for all views as in our assumption. However, the assumption also holds well for a close neighborhood around the point.

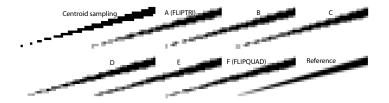

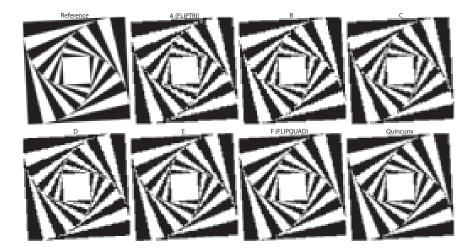

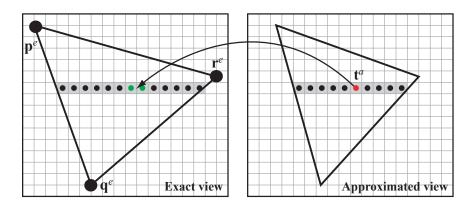

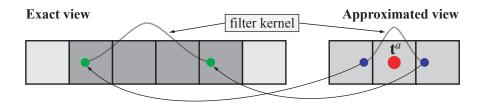

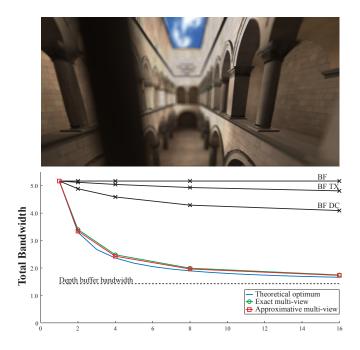

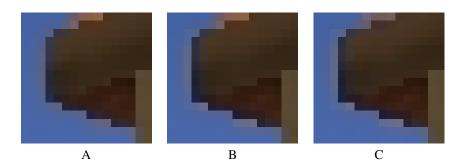

We present two versions of the rasterization algorithm: one *exact* and one *approximate*. The exact version will produce the exact same result as rendering one view at a time, and consists of the sorted rasterization briefly described above. In itself the sorting will greatly improve performance of the texture cache which is already used in all modern graphics hardware. The sorted rasterization traverses fragments which lie very close to each other on the surface of the triangle. Therefore, in the ideal case, the texture lookups will always be in the cache for all but the first of the views, and the texture bandwidth will be identical to single-view rendering. We will never quite reach the ideal case, but our evaluation shows that our algorithm gives close to constant texture bandwidth for between 2 and 16 viewpoints. The ocean scene does not perform as well, but this is only to be expected since it is a very hard case given our initial assumption.

Although our exact algorithm greatly reduces texture bandwidth, it still requires that we execute the pixel shader for every pixel and every viewpoint, and this can become very costly. In our approximate extension, we start from our exact algorithm and add a cache that stores results of pixel shader evaluations. Each time we process a fragment, we query the cache to see if we find one or more pixel shader evaluations in "close enough" vicinity of the current fragment. If we find appropriate cached results, we compute a color for the fragment by interpolation, and skip the pixel shader execution altogether. Whereas the exact algorithm only relies on our initial assumption to improve performance, this approximate extension relies on the same assumption for the correctness of the image. Therefore, as we show in our results, the performance of the approximate version will be the same for scenes with and without view-dependency. However, the approximate version will treat view-dependent effects as if we used single viewpoint rendering and therefore the rendered images may not be correct. If the viewer can perceive this incorrectness or not depends on the scene and spread of the viewpoints. The ocean scene, for example, has a highly distorted reflection, and therefore the viewer may not notice that it comes from a single viewpoint. If we use a flat mirroring surface instead, the viewer would immediately notice the loss of depth perception. Since the effects of approximation depend so heavily on surface properties, it is important to give the application programmer full control of when to use either the exact or approximate technique. The approximate algorithm can give substantial performance gains when used appropriately. In a stereoscopic rendering system, we observed that up to 95% of the fragments could be approximated for the secondary view.

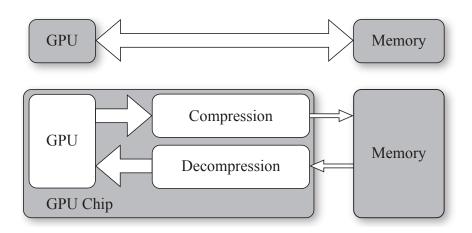

Figure 10: The top row shows a traditional GPU system without compression. Data is sent directly to memory over the bus. The bottom row shows a GPU using data compression. The GPU sends data to a compression unit and receives data from a decompression unit, both realized on the same hardware chip as the GPU. The compression unit compresses data before it is sent to memory, and the decompression unit decompresses data received from memory. Memory bandwidth usage is reduced if the data is successfully compressed.

## 4 Compression

Data compression is an optimization which focuses entirely on reducing memory bandwidth usage in a graphics system. An example of a GPU using data compression is shown in Figure 10. As can be seen, there are two new units, one that compresses and one that decompresses data, respectively. These units act as a communications channel between the GPU and main memory, and are typically implemented in hardware on the same chip die as the GPU. Compressing and decompressing data require computations, and one can therefore say that compression is a way of trading computational complexity for memory bandwidth.

In GPUs, the two dominating groups of compression algorithms are *texture compression* and *buffer compression*. Although these are quite similar, there are some key differences, of which the first is that buffers are continuously altered during rasterization while textures typically remain static. This has the effect that buffer compression and decompression must be a fairly symmetric operation since data must be both compressed and decompressed in real time when rendering an image. Texture compression on the other hand is an asymmetric process since textures are typically read-only during rendering. This means that the decompression algorithm must be inexpensive and realizable in real time, but the compression algorithm may be complex and slow to execute since the texture can be compressed and stored on disk prior to rendering.

Another difference that comes from the buffers being continuously altered is that buffer compression is much more sensitive to data loss. In texture compression, the image is compressed only once, and in addition, the application programmer has control over which textures she or he wish to compress. Therefore, most texture compression algorithms are *lossy*, and introduce some small error in the compressed image which is usually not visually disturbing. If the compression algorithm should produce a poor result for a particular image, the application programmer can just disable compression for that texture. Buffer compression on the other hand is much less predictable since the number of times a region of the screen is compressed and decompressed depends on the number of triangles rendered in that region. Repeated compression and decompression, so called *tandem compres*sion, can greatly amplify small errors in each compression step. Therefore, it is necessary to use *lossless* compression, or at least introduce some mechanism that allows the application programmer to control the total error introduced through compression. In any case, buffer compression algorithms always need a lossless fall-back for the case when the maximum allowed error is reached.

#### 4.1 Texture Compression

As can be seen in Figure 3, both the vertex and pixel shader share access to textures. It is therefore reasonable to assume that both the vertex and pixel shader may benefit from texture compression. However, in most cases, the pixel shader is more important since it will consume the vast majority of texture lookups.

As previously mentioned, texture compression is a highly asymmetric operation where compression can be allowed to take orders of magnitude more time than the decompression process. Although there are some cases which break this assumption, such as generating a cube-map by rendering to a texture, these are usually solved by disabling compression or treating texture as a buffer and use buffer compression algorithms [44]. Another important feature for texture compression is that a fixed bit rate is often crucial for efficiency. Typically, a texture image is divided into tiles (blocks) of pixels, and each tile is given a predetermined bit budget. For instance, the S3TC [19, 22] texture compression scheme divides the texture into  $4 \times 4$  pixel tiles, and each tile is stored using 64 bits of data according to a predetermined format. The reason for using a fixed bit rate is that random access to the texture must be supported. If fixed bit rate is used, it is easy to find the memory position of a tile in constant time. If variable bit rate is used instead, finding a tile requires searching from the beginning of the texture image, or looking up the memory position of the tile in some data structure [18]. These approaches require complex search algorithms to be implemented, and are typically less efficient than the simple approach used in fixed bit rate. This is the reason why variable bit rate has not been adopted in texture compression although it is known to give better image quality than fixed bit rate approaches.

Traditionally, texture images are stored in RGB (red-green-blue) color space with one value for each component. The value is typically in the range [0, 1], where 0

Base Exposure

LDR

HDR

Figure 11: These images show the difference between a low dynamic range (LDR) and high dynamic range (HDR) image when the exposure is changed. To the left, the image is shown with some base exposure. When the exposure of the LDR image is changed the image looks the same, just darker overall. In the HDR image, several new details, such as the column of light reflected in the water and the structure of the clouds, appear when the exposure is changed. These images are Copyright ©2004, Industrial Light & Magic, a division of Lucasfilm Entertainment Company Ltd.

indicates that the color channel is turned off, and 1 indicates that the color channel is at the maximum intensity that the screen can display. A problem with such images is that they are based on the properties of the screen, rather than true physical properties of a scene. This is illustrated in Figure 11, which shows an image with a widely varying range of the incoming luminance. There are some relatively dark areas on the trees and the sun is an extremely bright light source. A traditional *LDR* (low dynamic range) encoding of this image fails to accurately capture the whole range of the incoming luminance, which can be seen when the exposure is changed as in the middle image. If we use an alternative image encoding, called *HDR* or high dynamic range [11], we can accurately represent the whole range of incoming luminance. When we change the exposure of this image, as shown to the right in the figure, we can see that the details in the bright parts of the images have been captured.

As HDR images can represent a wider range of luminance, it is only fair to assume that they require more memory space and bandwidth for rendering. Whereas traditional textures are encoded with 8 bits per color channel, HDR textures are typically stored using 16 or 32 bits floating-point values per color channel. Despite this, at the time of writing, there is no support for HDR texture compression from graphics hardware vendors. This has perhaps hindered the development of HDR rendering somewhat since an uncompressed HDR texture requires 12 times the storage and memory bandwidth of a compressed LDR texture.

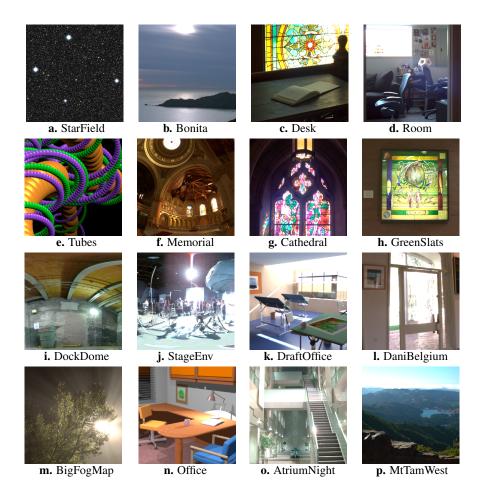

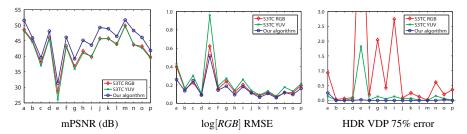

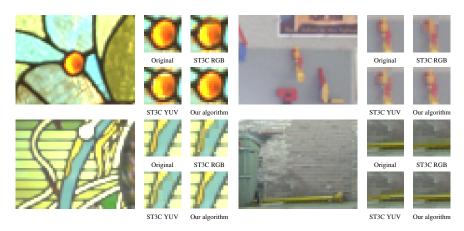

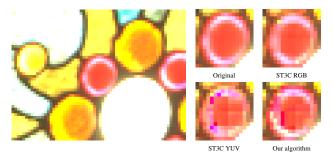

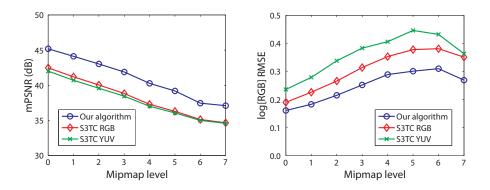

In Paper IV, we present the first texture compression format targeting HDR texture compression. Simultaneously Roimela et. al [38] also developed an HDR texture compression scheme, also published at the annual SIGGRAPH conference in 2006. These compression algorithms complement each other well as Roimela et. al focused on inexpensive hardware while we used a more expensive decompression algorithm that gives better image quality. Just like S3TC, both formats compress textures by six times. However, since the bit budget is larger for HDR images, we found that our algorithm gives less visual compression artifacts than S3TC in most cases. There have been several new algorithms on HDR texture compression [39, 47, 49], since we published our original algorithm, and although our algorithm remains rather computationally expensive, we see that it still performs very well in terms of visual quality when compared to its competitors. Recently, Microsoft published some information on their upcoming Direct3D 11 API [14], which contains a new HDR texture compression format called BC6. Unfortunately, at the time of writing, there is still no public information about how this format works, or how well it performs. We have also published an additional paper on practical HDR texture compression [29] of further details and findings which we were not able to fit into the original paper. That paper is not included in this thesis.

The paper on HDR texture compression was a joint collaboration between myself, Jacob Munkberg, Petrik Clarberg, and Tomas Akenine-Möller. I was not the primary author of this paper, but was active during the whole process. I contributed to the conceptual design of the algorithm, to some of the exhaustive search algorithms used for verification and some unreleased implementations. I also implemented and evaluated the extended versions of the S3TC compression algorithm, and co-authored in the writing and internal reviewing process of the paper.

#### 4.2 Buffer Compression

The most distinctive feature of buffer compression, when compared to texture compression, is that the contents of the buffer will constantly be modified whereas the texture is mostly static. Furthermore, buffer compression is often transparent to the application programmer, so she or he will not know if compression is enabled or not. Therefore, most buffer compression algorithms are lossless, since lossy compression could cause an application to behave unexpectedly, or generate errors that the programmer would not be aware of.

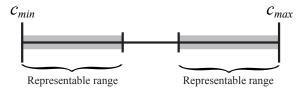

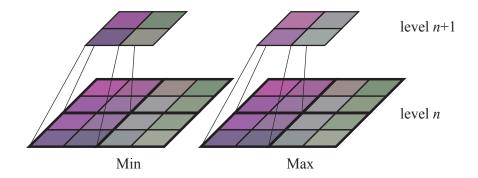

A shared requirement of both texture and buffer compression is that efficient random access must be supported. For texture compression this is solved using fixed bit rate, but this does not work for buffer compression since lossless compression cannot be guaranteed with fixed bit rate unless the original bit rate is used. Therefore, buffer compression uses variable bit rate encoding, and this is often realized by using a number of fixed bit rate modes. In particular, there is always a fall-back mode where tiles are stored in uncompressed form if all other compression modes fail to represent the data without loss. However, there remains the problem of variable bit rates and random memory access as described in Section 4.1. Variable bit rate requires searching through data structures to find the memory position of a tile, and this is not desirable. The most simple solution to this problem is to reserve enough memory to store an uncompressed version of each tile, as shown in Figure 12. This means that the compressed buffer will use the same amount of

| Tile 1                            | Tile 2 | Tile 3 | Tile 4 |  |  |  |

|-----------------------------------|--------|--------|--------|--|--|--|

| Uncompressed memory layout        |        |        |        |  |  |  |

| Tile 1   Tile 2   Tile 3   Tile 4 |        |        |        |  |  |  |

| Commenced managed in the second   |        |        |        |  |  |  |

Compressed memory layout

Figure 12: Buffer compression stores a data buffer tile by tile. For each tile sufficient memory is reserved to hold the uncompressed tile data, as this makes random accesses in the buffer efficient. A downside of this is that a compressed buffer will require as much memory as an uncompressed. However, we can still reduce memory bandwidth as we do not have to read or write more than the compressed data.

memory as an uncompressed buffer. However, less memory bandwidth is used by only writing and reading compressed data, and all the advantages of fixed bit rate compression are kept.

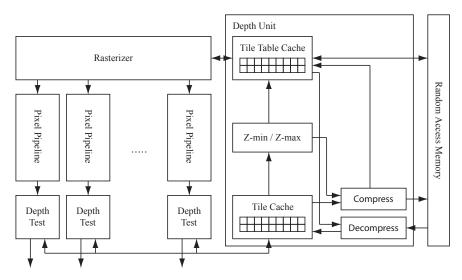

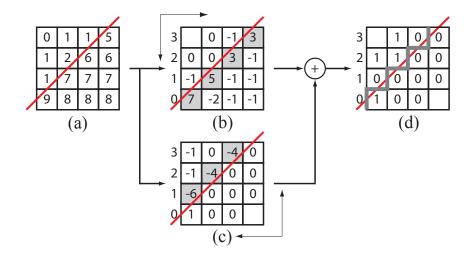

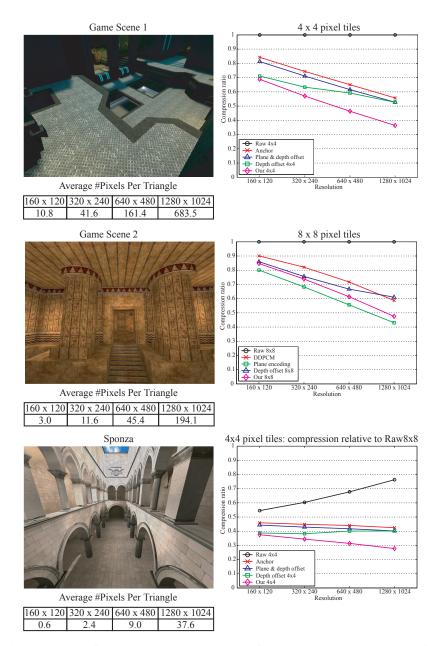

Buffer compression approaches have long been kept secret internally by the graphics hardware vendors, and very little information about them exists in academia. Our first paper on buffer compression, Paper V, is based on information we extracted from patent applications of the main graphics hardware vendors. We present in detail how a modern depth buffer architecture with compression and hierarchical depth culling (HDC) works [16], and it is reasonable to assume that color buffer architectures work in a very similar fashion. We also present a survey of the state of the art in depth buffer compression algorithms, and propose a novel depth compression algorithm of our own.

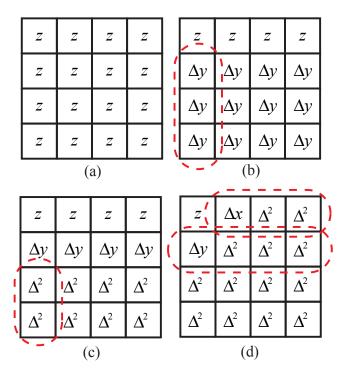

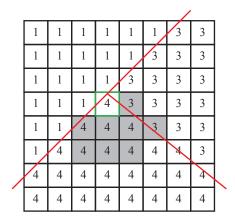

Our algorithm, just as most of the other depth compression algorithms, is based on representing a tile of pixels by one or more prediction planes, and to store small correction deltas which represent how much the actual pixel values deviate from the prediction planes. In particular, we found that previous work had missed a simple but efficient observation in the interpolation of the prediction plane, which makes it sufficient to use one-bit correction deltas instead of the two bits previously used. Although it is a simple observation, we save approximately one bit per pixel which is a significant gain. Furthermore, we also improve on previous approaches for coding multiple planes, and present robust one and two plane versions of our algorithm. The evaluation shows that our algorithm performs better than previous art, in particular for small tile sizes, such as  $4 \times 4$  pixels. We therefore believe it is well suited for use in mobile graphics devices.

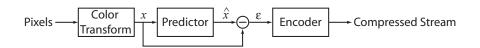

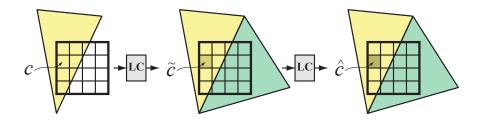

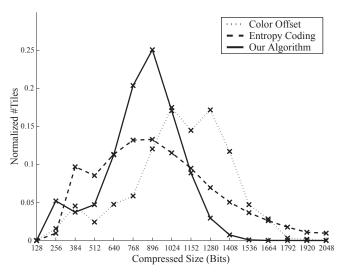

In our follow-up research, Paper VI, we similarly present a survey of existing color buffer compression algorithms, and present a compression algorithm of our own. The compression algorithm is based on the LOCO-I algorithm [48], but with modifications to make it more suitable for compressing small tiles, and on-the-fly compression. This algorithm differs somewhat from the depth compression approaches in that it is a variable bit rate entropy encoder. It is therefore not limited

to a fixed number of "trial and error" modes, but will rather produce the number of bits necessary to represent the tile. However, we still limited ourselves to a number of fixed sizes in the results. The reason for this is that the compressed size of a tile must be stored in an on-chip memory so that the GPU knows the number of bytes to read. If we allow arbitrary sizes, this memory becomes very large, and furthermore the width of the memory bus will limit which sizes that are practical to read anyway.

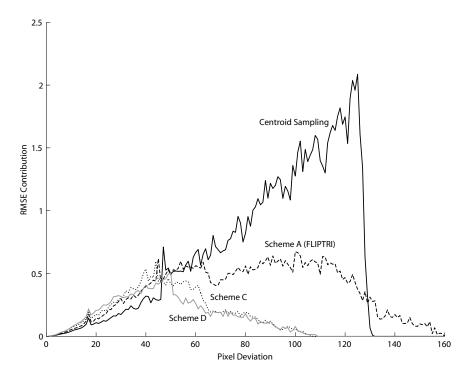

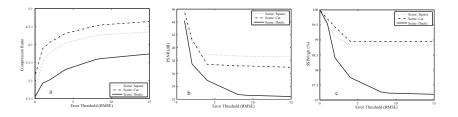

In this paper we also present the concept of lossy buffer compression. This is a sensitive subject since buffer compression so far has been transparent to the application programmer. However, it makes sense to give the application programmer a way to control the accepted compression loss, and we can easily solve backwards capability problems by allowing no error by default. In the paper, we propose a mechanism to track the total error of a tile, including possible errors introduced through tandem compression, and guarantee that it never exceeds a given threshold value. Although it would be nice to be able to track and control the maximum pixel error, we noted that such a system is much too conservative for practical use. We therefore settle for controlling the maximum allowed *RMSE* (root mean square error) over a tile. Our results show great bandwidth reductions for lossy compression, with an often negligible quality decrease. However, we found some hard cases in which color leakage may lead to visual artifacts.

The paper on color buffer compression was co-authored with Jim Rasmusson and Tomas Akenine-Möller. Although I was not the primary author of this paper, I contributed significantly to it. Both Jim and myself were active in all parts of writing the paper and implementation, although I was more involved in the implementation of the lossless codec, and Jim focused more on the lossy compression aspect.

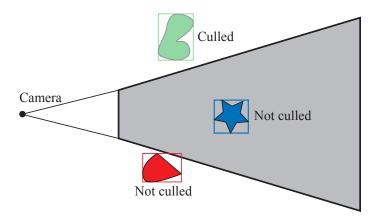

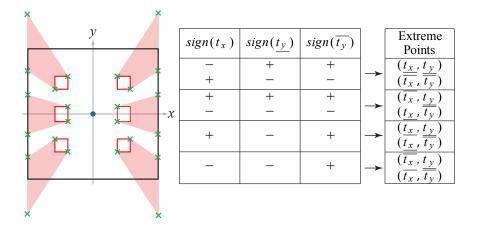

## 5 Culling

Generally speaking, *culling* in computer graphics is when we use a simple test to determine if we need to run a complex computation or not. If the test indicates that the computation will not contribute to the final image it can safely be skipped, and consequently performance is improved. A typical example of this is view frustum culling, shown in Figure 13. Here, a complex object is represented by a simple bounding box. If the bounding box is not visible from the camera's point of view, then the same is true for the entire object. Using this simple test, we can quickly skip rasterization of the whole object, and thereby gain performance. It should be noted that culling algorithms often are *conservative*. That is, they may give false negatives, such as the red object in Figure 13 which is incorrectly classified as visible. However, they may never incorrectly cull something which is visible. Whereas a false negative will only affect performance, incorrect culling may give errors in the rendered image.

Current graphics hardware supports a number of fixed-function culling algorithms,

Figure 13: An illustration of view frustum culling, where a bounding box is used to represent each object in the scene. If the bounding box is not visible from the camera, the object is culled. As can be seen for the red object, the algorithm may falsely classify an invisible object as visible. However, a visible object will never be culled, which is important since this could give errors in the rendered image.

such as view frustum culling [6], back-face culling [4], and hierarchical depth culling [16]. However, a great problem is that the graphics hardware becomes more and more programmable while the culling algorithms have stayed the same. This leads to a mismatch between culling and programmability. For example, if we implement a new lighting algorithm in a pixel shader program, it would be nice to add culling to improve its performance. However, in order to do so we must to reformulate our new culling algorithm to fit into any of the aforementioned fixed function-culling algorithms. This is not always possible, or is often so complex that it leads to a decrease in performance when compared to not using culling.

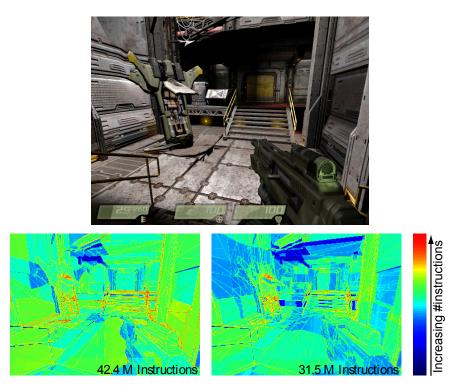

In this thesis, we introduce the concept of *programmable culling*. By analyzing the pixel and vertex shader programs it is possible to automatically generate a *cull shader program* that can be executed for a set of pixels, or a set of vertices. The cull shader program determines if the set of pixels or vertices can safely be discarded without affecting the final image, and if such is the case we gain performance by not having to execute the pixel or vertex shader. There are two main benefits with our programmable culling approach which we believe makes it very attractive. First, the absence of culling will not effect the final image, only the performance. This means that if a hardware vendor chose not to implement programmable culling, or to only implement a subset of it to support some culling algorithms, it will only affect performance and will not break applications that rely on programmable culling. Second, our programmable culling fits well into the current rasterization pipeline. It can therefore be implemented with minimal-or even no changes in current APIs. This makes it both transparent to the application programmer, and makes it simple to ensure backwards compatibility.