| Outline              |                      |   |     |

|----------------------|----------------------|---|-----|

| Basic Aspects        |                      |   |     |

| An Example           |                      |   |     |

| The VHDL Simulation  | Mechanism            |   |     |

| Signal Assignment an | d Delay Mechanisms   |   |     |

| VHDL for System Syn  | thesis               |   |     |

|                      |                      |   | Ä   |

| Kris Kuchcinski      | Introduction to VHDL | 1 | LUN |

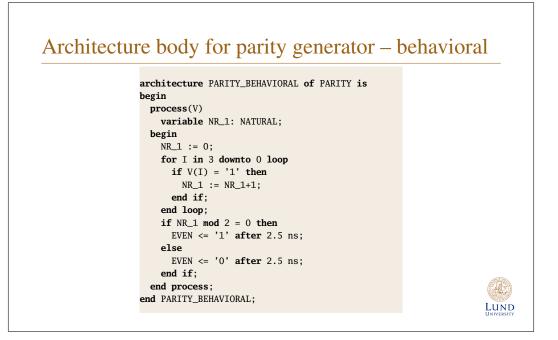

| An Exan         | nple                                                                                                 |   |    |

|-----------------|------------------------------------------------------------------------------------------------------|---|----|

|                 | Example                                                                                              |   |    |

|                 | A four bit parity generator                                                                          |   |    |

|                 | <pre>entity PARITY is     port(V:in BIT_VECTOR(3 downto 0);         EVEN:out BIT); end PARITY;</pre> |   |    |

| Kris Kuchcinski | Introduction to VHDL                                                                                 | 5 | Lu |

### The VHDL Simulation Mechanism

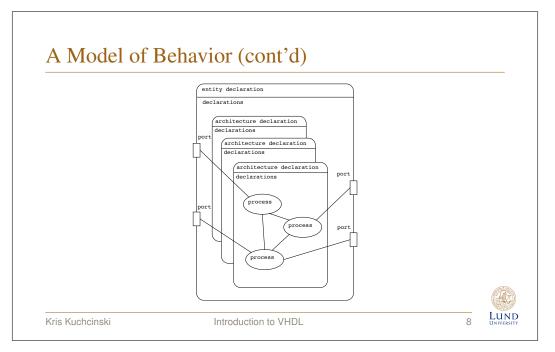

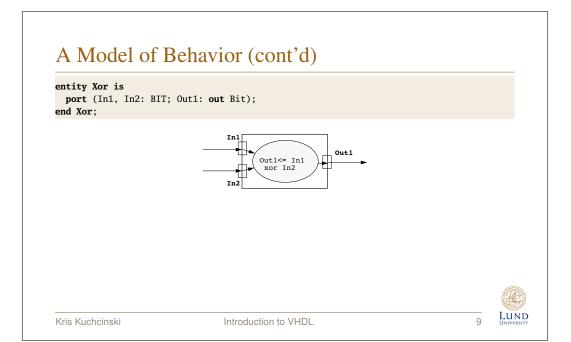

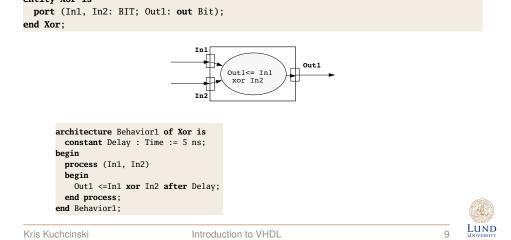

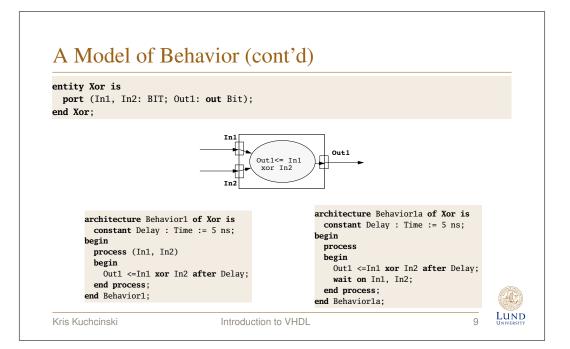

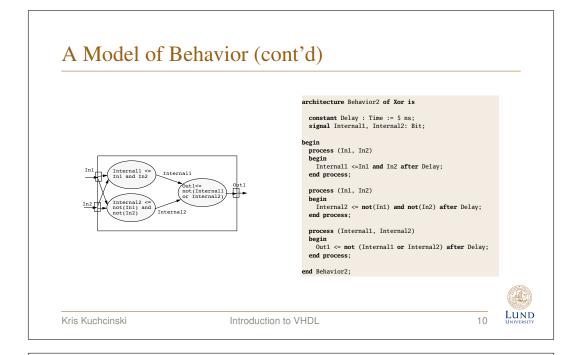

# A Model of Behavior (cont'd)

# Example (cont'd)

| <b>I</b> ``     |                                                                                                                                                                  |    |     |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

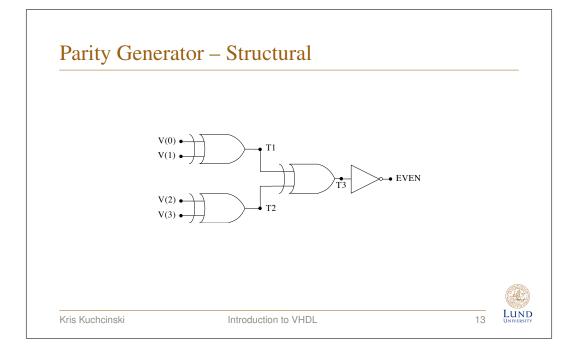

|                 | <pre>use WORK.all;<br/>architecture PARITY_STRUCTURAL of PARITY is<br/>component XOR_GATE</pre>                                                                  |    |     |

|                 | <pre>port(X,Y: in BIT; Z: out BIT);<br/>end component;</pre>                                                                                                     |    |     |

|                 | <pre>component INV   generic(DEL: TIME);   port(X: in BIT; Z: out BIT); end component;</pre>                                                                     |    |     |

|                 | signal T1, T2, T3: BIT;                                                                                                                                          |    |     |

|                 | <pre>begin    XOR1: XOR_GATE port map (V(0), V(1), T1);    XOR2: XOR_GATE port map (V(2), V(3), T2);    XOR3: XOR_GATE port map (T1, T2, T3);    INV1: INV</pre> |    |     |

|                 | <pre>generic map (0.5 ns) port map (T3, EVEN); end PARITY_STRUCTURAL;</pre>                                                                                      |    |     |

| Kris Kuchcinski | Introduction to VHDL                                                                                                                                             | 14 | LUN |

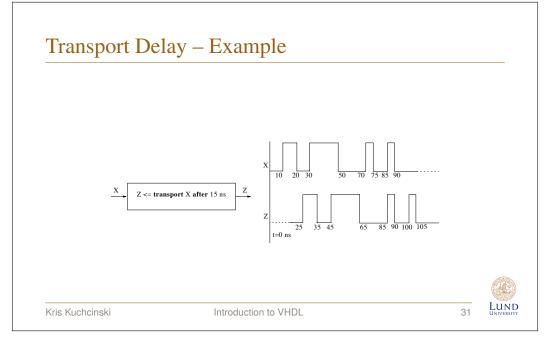

### Signal Assignment and Delay Mechanisms

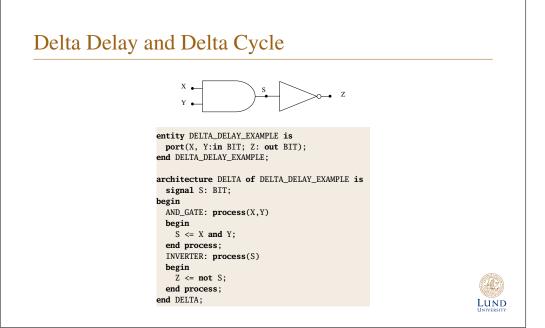

# The VHDL Simulation Mechanism

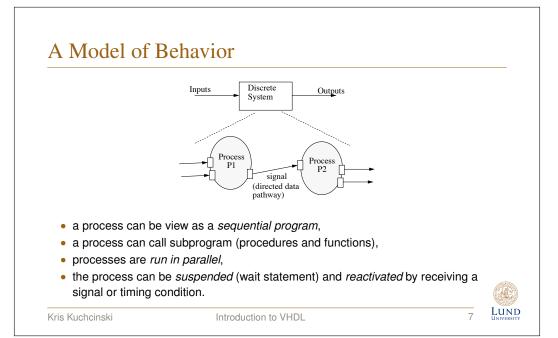

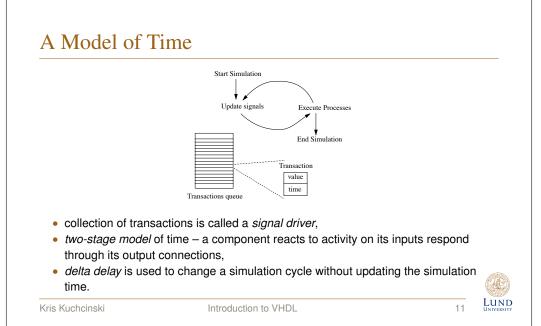

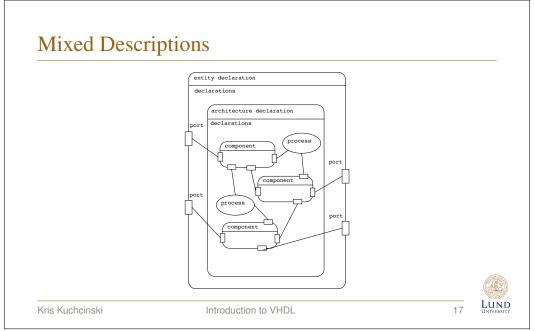

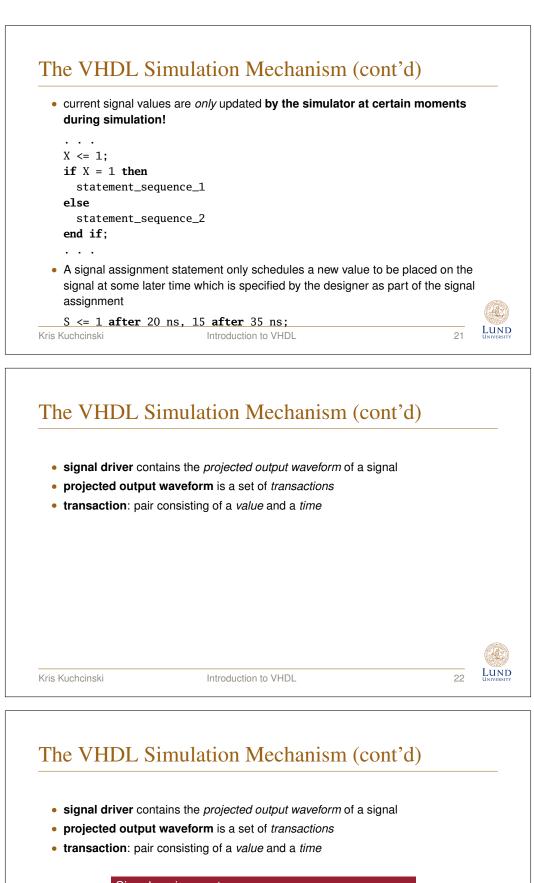

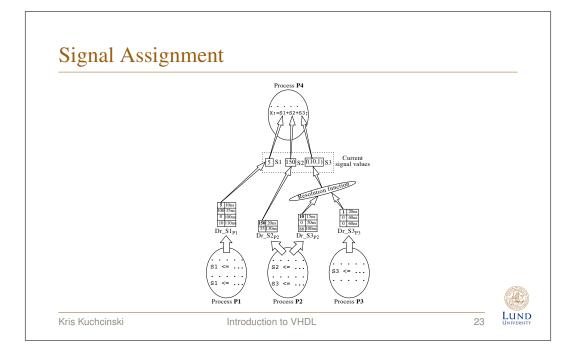

- After *elaboration* of a VHDL model results a set of processes connected through signals.

- The VHDL model is simulated under control of an event driven simulation kernel (*the VHDL simulator*).

- Simulation is a cyclic process; each *simulation cycle* consists of a signal update and a process execution phase.

- A global clock holds the *current simulation time*; as part of the simulation cycle this clock is incremented with discrete values.

Kris Kuchcinski

| A signal assignment only affects the projected output<br>waveform, by placing one or more transactions into the<br>driver corresponding to the signal and possibly by<br>deleting other transactions. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Kris Kuchcinski

Introduction to VHDL

# The VHDL Simulation Cycle

- The current time T<sub>c</sub> is set to T<sub>n</sub>

- Each active signal is updated; as result of signal updates events are generated

- Each process that was suspended waiting on signal events that occurred in this simulation cycle resumes; processes also resume which were waiting for a certain, completed, time to elapse

- Each resumed process executes until it suspends

- The time *T<sub>n</sub>* of the next simulation cycle is determined as the earliest of the following three time values:

- 1. TIME'HIGH

- 2. The next time at which a driver becomes active

- 3. The next time at which a process resumes

Kris Kuchcinski

Introduction to VHDL

LUND

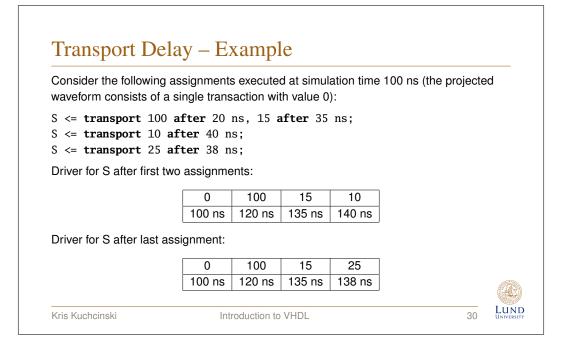

# Signal Assignment Statement furging signment statement furging f

# Signal Assignment Statement

The projected output waveform stored in the driver of a signal can be modified by a

signal assignment statement.

signal\_assignment\_statement ::=

target <= [transport |

[reject time\_expression] inertial] waveform;</pre>

waveform ::= waveform\_element {, waveform\_element}

waveform\_element ::= value\_expression [after time\_expression]

S <= transport 100 after 20 ns, 15 after 35 ns; S <= 1 after 20 ns,15 after 35 ns;</pre>

The concrete way a driver is updated as result of a signal assignment depends on the delay mechanism.

Kris Kuchcinski

Introduction to VHDL

28 LUND

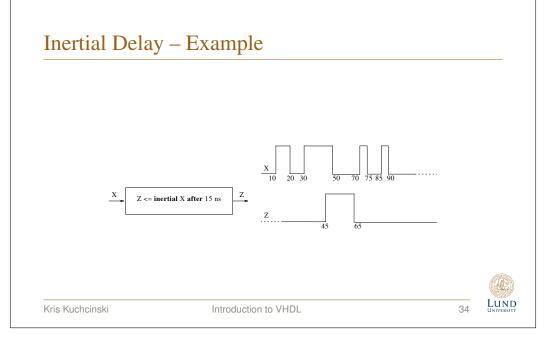

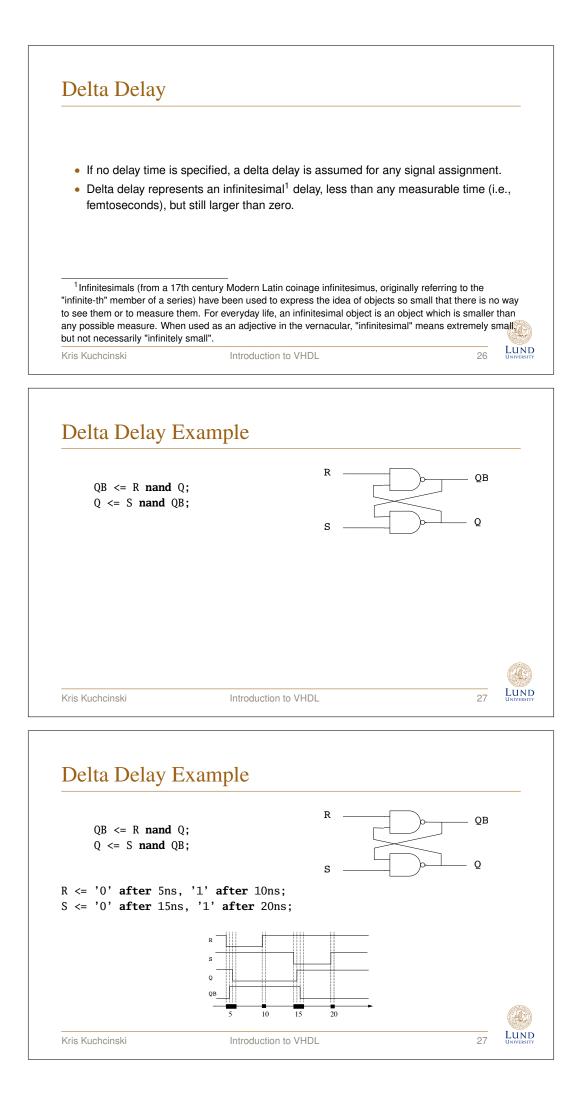

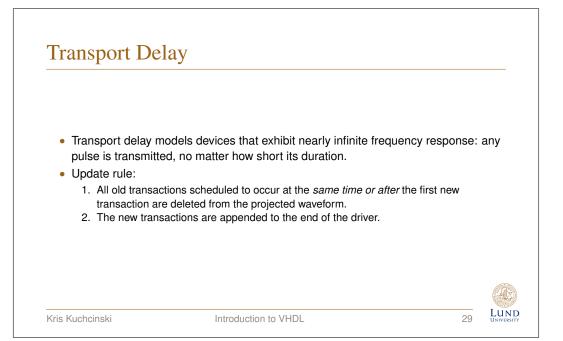

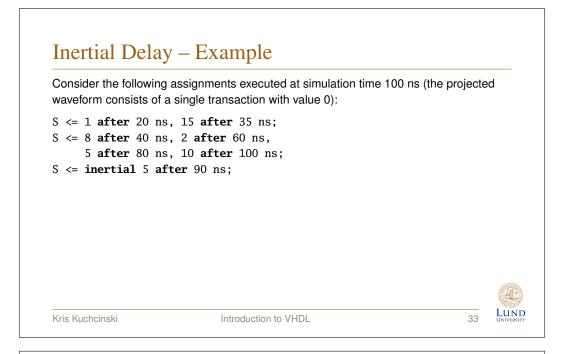

### Inertial Delay

- Inertial delay models the timing behaviour of current switching circuits: an input value must be stable for a duration before the value propagates to the output.

- Additional update rule (after operations have been performed like for transport delay):

- all old transactions scheduled to occur *before* the first new transaction are deleted from the projected waveform

- accepted are those transactions which are immediately preceding the first new transaction and have the same value with it

## Inertial Delay – Example

Consider the following assignments executed at simulation time 100 ns (the projected waveform consists of a single transaction with value 0):

$S \le 1 \text{ after } 20 \text{ ns, } 15 \text{ after } 35 \text{ ns;}$   $S \le 8 \text{ after } 40 \text{ ns, } 2 \text{ after } 60 \text{ ns,}$  5 after 80 ns, 10 after 100 ns;  $S \le \text{ inertial } 5 \text{ after } 90 \text{ ns;}$  $1^{st} \text{ assignment: } \boxed{\begin{array}{c|c} 0 & 1 & 15 \\ 100 \text{ ns } & 120 \text{ ns } & 135 \text{ ns} \end{array}}$

Kris Kuchcinski

Introduction to VHDL

LUND

33

### Inertial Delay – Example

Consider the following assignments executed at simulation time 100 ns (the projected waveform consists of a single transaction with value 0):

| <pre>S &lt;= 1 after 2 S &lt;= 8 after 4</pre> | 0 ns, 2<br>0 ns, 10  | <b>after</b> 6<br>) <b>after</b> | 0 ns,  |        |        |    |  |   |

|------------------------------------------------|----------------------|----------------------------------|--------|--------|--------|----|--|---|

| 1 <sup>st</sup> assignment:                    | 0                    | 1                                | 15     |        |        |    |  |   |

|                                                | 100 ns               | 120 ns                           | 135 ns |        |        |    |  |   |

| 2 <sup>nd</sup> assignment:                    | 0                    | 8                                | 2      | 5      | 10     |    |  |   |

|                                                | 100 ns               | 140 ns                           | 160 ns | 180 ns | 200 ns |    |  |   |

|                                                |                      |                                  |        |        |        |    |  |   |

|                                                |                      |                                  |        |        |        |    |  | Ä |

| Kris Kuchcinski                                | Introduction to VHDL |                                  |        |        |        | 33 |  |   |

| Consider the follo<br>waveform consist |          | 0              |          |        | ion time 1 | 100 ns (the projected |

|----------------------------------------|----------|----------------|----------|--------|------------|-----------------------|

| S <= 1 <b>after</b> 2                  | 0 ns, 15 | 5 <b>after</b> | 35 ns;   |        |            |                       |

| S <= 8 after 4                         |          |                |          |        |            |                       |

| 5 <b>after</b> 8                       | 0 ns, 10 | ) after        | 100 ns;  |        |            |                       |

| S <= inertial                          | 5 after  | 90 ns;         |          |        |            |                       |

|                                        |          |                |          |        |            |                       |

| 1 <sup>st</sup> assignment:            | 0        | 1              | 15       |        |            |                       |

| 10 assignment.                         | 100 ns   | 120 ns         | 135 ns   |        |            |                       |

| 2 <sup>nd</sup> assignment:            | 0        | 8              | 2        | 5      | 10         |                       |

|                                        | 100 ns   | 140 ns         | 160 ns   | 180 ns | 200 ns     |                       |

| and the second                         |          | _              | <b>–</b> |        |            |                       |

| 3 <sup>rd</sup> assignment:            | 0        | 5              | 5        |        |            |                       |